應用于時序控制芯片之內存測試解決方案

隨著行動裝置影像顯示與畫質日漸演進,行動裝置亦引進8K / 4K等高畫質的顯示,并應用于攝影、游戲和用戶接口,促使影像傳輸帶寬和速度要求大增。更有大尺寸面板也相繼提供高畫質面板于電視裝置上,以4K畫質而言,其面板的優勢和價值在50吋及以上的電視中更容易體現。日本政府更計劃于2020年奧運期間提供8K高畫質的視訊轉播。在此規劃下,面板規格勢必也得向上提升。隨著邁向高畫質紀元,時序控制芯片 (T-CON Chip; Timing Controller Chip) 也需提升其所支持的分辨率,處理高畫質畫面相關數據,進而將完美的畫面呈現于面板上。

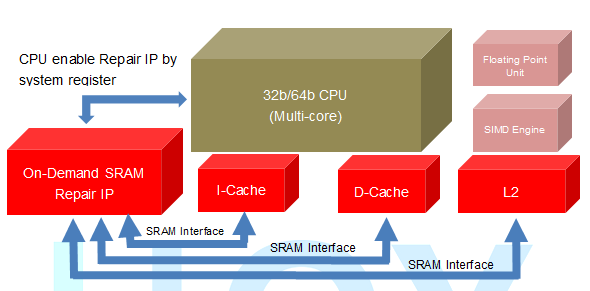

當對畫質 (Resolution) 的要求愈來愈高,相對需要處理的數據量也隨之提升,以4K畫質為例,其分辨率是FHD (2K×1K) 的四倍。為了節省影像傳輸接口的帶寬耗損,因此時序控制芯片內多半會內建SRAM內存,此一內存用來暫存已經傳送到時序控制芯片驅動器,但尚未要透過時序控制芯片驅動器進行輸出的影像數據。由于面板的尺寸愈來愈高、分辨率愈來愈高、畫面更新率、色澤也都在提升,因此,時序控制芯片內的SRAM內存將不斷的加大容量,好因應愈來愈大的影像數據傳輸量與處理量。

當內建SRAM容量愈來愈大時,相對時序控制芯片制造的成本也隨之增加。更多的SRAM內存容量就意味著更大的芯片面積。且隨著效能與耗電的要求更加嚴謹,芯片的制程也就愈往高階制程邁進。伴隨而來的問題,就是芯片良率以及工作可靠度的影響。先進制程與愈來愈大的內存需求,成為時序控制芯片制造端的不穩定因素。

為確保時序控制芯片上的內存工作正常,內建自我測試技術 (BIST; Built-In Self -Test) 成為芯片實作中,不可或缺的一部分。自我測試電路 (Built-In Self-Test),可以提高測試的錯誤涵蓋率,縮短設計周期,增加產品可靠度,并加快產品的上市速度。由于傳統的測試做法是針對單一嵌入式內存開發嵌入式測試電路,所以會導致時序控制芯片面積過大與測試時間過久的問題,進而增加時序控制芯片設計產生的測試費用與銷售成本。另外,傳統內存測試方法無法針對一些缺陷類型而彈性選擇內存測試的算法,將導致內存測試結果不準確。有鑒于此,厚翼科技特別開發「整合性內存自我測試電路產生環境-Brains」,以解決傳統設計之不足。本文將針對時序控制芯片應用,結合厚翼科技所開發之「整合性內存自我測試電路產生環境-Brains」,搭配實作案例跟讀者們分享。

實作案例

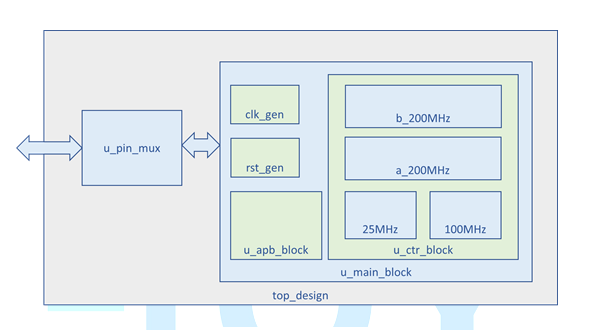

以下將以時序控制芯片應用實作案例,介紹如何透過Brains自動化產生相關內存測試電路,以解決內存所造成良率下降問題。此案例所使用的制程為130nm,圖一是該案例簡略架構圖,此架構明確地將芯片IO部分與主要功能部分切開來,并透過Pin Mux功能,來節省芯片頂層所需的控制腳位。在主要功能部分,共有四個Clock Domain,各別Clock Domain下,各自包含了不同種類的內存于其中。針對這些內存,我們透過Brains自動化的產生相對應之內存測試電路。

圖一 T-CON案例簡略架構圖

此案例中,針對內存測試的需求,包含了:全速測試模式 (At-Speed Testing),Bypass功能以及自動分群 (Auto Grouping)。其中的Bypass功能,主要是用來提升DFT Test Coverage。當透過Scan Chain做測試時,由于無法觀測到內存內部數值,所以整體芯片Test Coverage會受影響。Brains所支持的Bypass功能,即是用來補足此點。該功能將內存的輸入端及輸出端進行異或處理,并可根據需求,選擇是否使用緩存器來儲存數值。藉此,可在Scan Chain測試模式下,提升整體芯片Test Coverage。

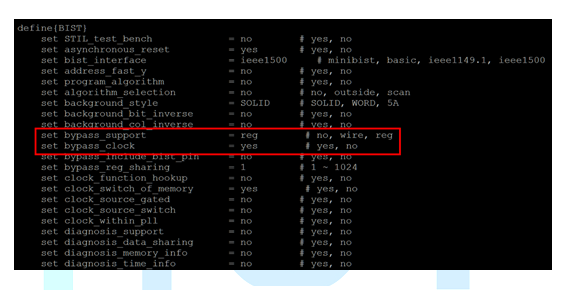

由于不同的設計項目及應用,對于內存測試的需求不盡相同。因此,Brains將不同的設計需求,以選項的方式呈現。使用者可根據不同的需求,選擇所需的功能。圖二為Brains功能選擇范例檔案 (Brains Feature List, BFL)。其中紅色框線的部分,即是用來選擇Bypass功能是否要支持。

圖二 Brains功能選擇范例檔案

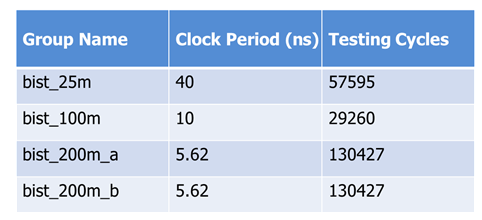

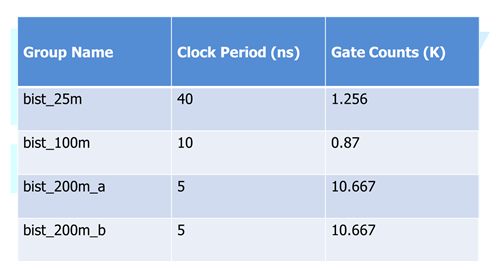

此案例總共使用到148個內存,其類型包含了Single-Port SRAM,Dual-Port SRAM以及Two-Port SRAM。透過Brains所支持的內存自動辨識功能,用戶只需將內存模塊的Behavior Model (Verilog file) 指定到Brains中,則可輕易地將設計項目中所用到的內存模塊辨識出來。再搭配Brains所支持的Clock Tracing功能,從內存模塊的Clock訊號,往上層追溯,直到該設計項目的Clock Root點,即可自動地將內存模塊歸類到各自所屬的Clock Domain下。表一為自動分群之后的分群架構,共有四個BIST Controller,各別針對其所屬之內存模塊來進行控制與測試。而詳細的分群架構,則會記錄在Brains所產出之BRAINS_memory_spec.meminfo檔案中,該檔案記錄各個BIST Controller中,關于Sequencer和Group的架構,如圖三所示。

表一 內存自動分群結果

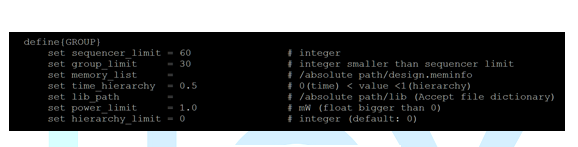

圖三 BRAINS_memory_spec.meminfo范例檔案

由圖三可得知,單一Clock Domain下,會包含Controller, Sequencer等架構,而Sequencer下則會根據BFL中關于Group的定義來劃分Group的架構,相關設定如圖四所示。其中sequencer_limit選項用來設定單一Sequencer下,所支持最多Group數。而group_limit選項則是用來設定單一Group下,所支持最多內存模塊數目。

圖四 BFL中Grouping相關設定

實作結果

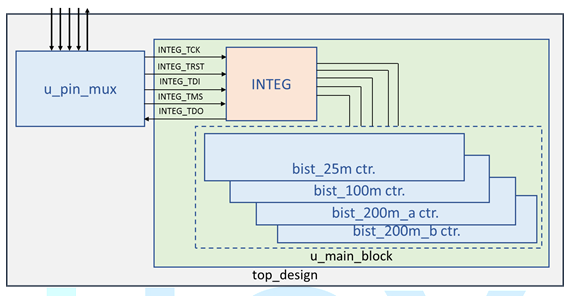

當Brains執行完畢后,則會產生相對應檔案。其中包含BIST 電路檔案 (Verilog file) 、相關合成模擬執行檔案 (TCL file) 以及加入BIST電路后的完整設計檔案 (Final RTL Design; Verilog file)。圖五為加入BIST電路后,完整的設計項目架構。

從圖五可得知,此實作案例最后會由一組JTAG接口,來控制整個BIST測試的流程。單一JTAG接口的控制方式,可節省芯片頂層的腳位數目,且標準JTAG接口,也方便與其它功能整合。

圖五 實作結果架構圖

當相關電路產生完畢后,需要透過仿真來驗證功能性是否完好。Brains除了產生相對應的仿真程序外,也會額外產生包含有Fault Bits的預先埋錯內存模塊 (Faulty Memory Model)。此預先埋錯內存模塊主要用來驗證Brains所產生的BIST電路功能正確與否。表二為各個Clock Domain執行模擬驗證時所需花費的時間。

除了仿真時間之外,所產生的BIST電路面積,通常也是芯片設計實作中,考慮的因素之一。表三為BIST電路合成完之面積結果,全部的BIST電路占約23K Gate Counts。以此案例之T-CON芯片所含148個內存數目來比,BIST電路所占之芯片面積相當渺小。

表二 模擬時間結果

表三 BIST電路面積結果

總結

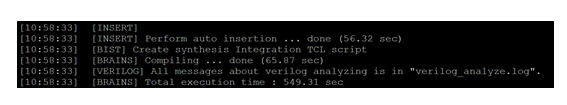

因應高畫質世代來臨,時序控制芯片內含之內存數量勢必愈來愈多,此時,內存測試解決方案亦成為芯片設計中不可或缺的一環。藉由Brains自動化產生相對應的內存測試電路,對用戶來講,不需太過繁復的設定過程,即可完成內存測試解決方案的實作。以此案例為例,單純Brains運行的時間,只需約九分鐘的時間 (如圖六所示) 就能完成內存測試解決方案的實作。對于分秒必爭的ASIC實作時程來說,可節省相當大的時間。除此之外,Brains彈性的設定選項,以及基于自有專利所建構的硬件電路,都是用戶在實作內存測試解決方案的一大利器。

圖六 Brains實作時間信息

關于厚翼科技

厚翼科技基于多項內存測試相關專利,致力于創新的各類的內存測試技術的研發,以便對全球快速成長的系統芯片架構提供更可靠的內存測試服務。現今各種電子產品功能日趨復雜,系統芯片設計需要更多的內存,系統芯片設計廠商正面臨著產品對成本與節能等各方面的需求。厚翼科技所創新的可程序化暨管線式架構內存測試技術提供給用戶能夠建構出特有的優化內存測試方式。厚翼科技的核心技術在于特有的可程序化暨管線式架構內存測試技術,并且透過各項專利加以保護。厚翼科技能夠和使用者緊密合作與提供技術支持,以便協助使用者完成高質量設計,增加產品競爭力。 展望競爭激烈的電子系統產品市場,當你計劃架構新的系統芯片應用產品時,厚翼科技憑借其高效能、低功耗可程序化暨管線式架構內存測試技術,能夠協助你的團隊有效的控制產品成本,打敗競爭對手。

評論