理解并滿足FPGA電源要求(上)

靈活的FPGA實現(xiàn)方案具有很多優(yōu)勢但也面臨很大的挑戰(zhàn):為FPGA供電以確保無縫工作。本白皮書旨在找到是什 么原因?qū)е?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/FPGA">FPGA供電越來越復(fù)雜,介紹設(shè)計FPGA電源樹時 必須要綜合考慮的問題,研究FPGA電源為什么是真正的系 統(tǒng)級問題,這一系統(tǒng)級問題為什么日益突出。

1 是什么決定了FPGA電源要求?

FPGA的功耗需求是由固定的和變化的兩種因素綜合決 定的:工藝技術(shù)和硅片設(shè)計所帶來的靜態(tài)功耗,以及每一設(shè) 計獨特的應(yīng)用所帶來的動態(tài)功耗。動態(tài)功耗是每一資源具體的使用及其使用量的產(chǎn)物, 與信號觸發(fā)和電容負(fù)載充放電導(dǎo)致的額外功耗有關(guān)。結(jié)果, 負(fù)載較重的FPGA設(shè)計和具有較高時鐘頻率的設(shè)計通常功耗 更大一些。例如,使用通用I/O和高速串行收發(fā)器時,所使 用的I/O標(biāo)準(zhǔn)以及預(yù)期的數(shù)據(jù)速率等因素會確定I/O觸發(fā)速 率,以及邏輯時鐘速率,因此,這類收發(fā)器會影響總電源需 求。正如預(yù)期,數(shù)據(jù)速率越快,所需要的時鐘頻率越高,負(fù) 載就必須以更快的頻率充放電,因此,功耗也就越高。由 于多種因素確定了FPGA的電源要求,因此,不同的FPGA系 列,即使是完全相同的FPGA在不同的應(yīng)用環(huán)境下,電源要 求都會各不相同。

理解FPG A設(shè)計的電源要求會非常復(fù)雜, 但是也非常 重要,因此,大部分FPGA供應(yīng)商都會提供功耗估算工具。 Altera提供了全套的PowerPlay功耗分析工具,包括PowerPlay 早期功耗估算器表單,用于在設(shè)計早期階段估算FPGA系統(tǒng) 的功耗,以及嵌入在Altera Quartus? II軟件中的PowerPlay功耗 分析器工具,在設(shè)計完成后輸出比較準(zhǔn)確的功耗分析結(jié)果,

以確保不會打破散熱和供電預(yù)算。

2 將FPGA功耗轉(zhuǎn)換為電源轉(zhuǎn)換器要求

理解FPGA每一電源軌最初的功耗要求只是設(shè)計合適的 電源樹的第一步;考慮到具體的資源使用情況,還應(yīng)該評估 其他的需求和考慮,才能進(jìn)一步提高設(shè)計性能。

3 內(nèi)核電源

FPGA上功耗最大的輸入一般是內(nèi)核電源軌,通常標(biāo)記 為VCC。這是可以理解的,因為內(nèi)核電源軌驅(qū)動邏輯,其使 用是任何FPGA設(shè)計的關(guān)鍵所在。由于FPGA所包含的邏輯量 達(dá)到了極高的水平,因此,功耗需求會不斷增長。例如, Altera最新的第10代FPG A和SoC, Arr ia? 10和 Stratix ? 10系列,充分發(fā)揮其高密度特性以及相關(guān)的小工藝 尺寸優(yōu)勢, 器件的邏輯單元數(shù)量高達(dá)1百萬(LE)以上。 雖然 每 一 邏 輯 單 元 的 功耗 要 低 于 前 一 代 , 但 是 , 資 源 利 用 率 很 高 的 高 頻 設(shè) 計 的 內(nèi) 核 電 流會超過100 A。

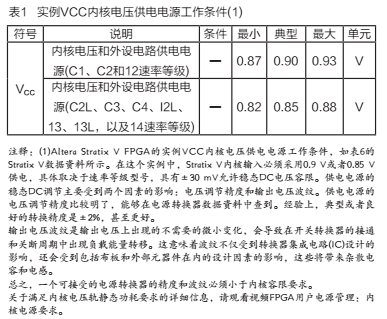

除 了 要 滿 足 大 功 率 需 求 , 內(nèi) 核供 電 電源 還 必 須 滿 足 嚴(yán) 格 的穩(wěn) 態(tài) 和 瞬 變 電 源 軌 要 求 。 穩(wěn) 態(tài) 要 求 是 指 , 不

論 內(nèi) 核 邏 輯 怎 樣 工 作 , 都 能 夠 維 持 內(nèi) 核 輸入的穩(wěn)態(tài)DC電壓, 或 者 , 簡 言 之 , 供 電 電 源 與 內(nèi) 核 輸 入 電 壓 的 穩(wěn) 壓 精 度 有 多 高 。 正如表1所述,通常能 夠在數(shù)據(jù)資料或者DC 工 作 特 性 中 找 到 某 一 FPGA的實際要求,預(yù) 期 的 V C C 電 壓 值 被 表 示 為 容 限 —— 最 小 和 最大偏離。隨著FPGA 技 術(shù) 向 更 小 工 藝 節(jié) 點 的 邁 進(jìn) , 所 允 許 的 容限在減小,理解并考慮好內(nèi)核電源軌供電也越來越重要。

內(nèi)核電源軌的動態(tài)負(fù)載要求是由FPGA快速加載和釋放 資源的能力決定的,這會導(dǎo)致當(dāng)前的輸入電源要求出現(xiàn)很大 而且很快的變化。例如,如果需要非常多的邏輯來實現(xiàn)一項 功能,將極大的改變內(nèi)核輸入的動態(tài)功耗。靠近每一FPGA 電源軌會有體電容,目的是在負(fù)載變化時提供瞬變電流;但 是,內(nèi)核電源軌所使用的供電電源的瞬時響應(yīng)也必須能夠迅 速調(diào)整適應(yīng)負(fù)載的變化,以確保電源軌電壓保持在可接受的 范圍內(nèi),體電容可以再充電。對于內(nèi)核電源軌,實現(xiàn)體電容 和電源轉(zhuǎn)換器快速瞬時響應(yīng)的均衡尤其關(guān)鍵。

內(nèi)核電源軌理想的電源轉(zhuǎn)換器應(yīng)能夠同時實現(xiàn)較高的 調(diào)節(jié)精度、低波紋和快速瞬時響應(yīng)。滿足這些要求的一種方法是使用具有較高開關(guān)頻率的開關(guān)轉(zhuǎn)換器,這有很多優(yōu)點。首先,較高的開關(guān)頻率支持使用體積較小的小電感和電容,

(1a) 之前 之后

(1c)之前 之后

圖1 使用Enpirion PowerSoC解決方案

在 C y c l o n e V S o C 開 發(fā) 套 件 上 采 用 E n p i r i o n PowerSoC解決方案替代現(xiàn)有的供電電源解決方 案,供電電源引腳布局減小了22% (1a),功耗降 低了35% (1b),去掉了昂貴的鉭電容,所需的體 電容減少了一半,從而減小了體積,降低了成本 (1c)。

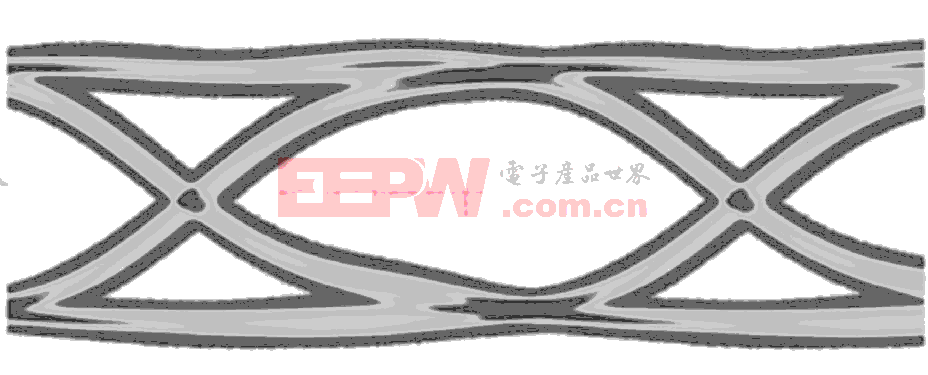

圖2 眼圖

Stratix V GX FPGA電路板上11.3 Gbps信號的眼圖。使用了一片EN6337QI Enpirion

PowerSoC,將VCCRT_GXB和VCCA_GXB收發(fā)器引腳的VIN = 3.3 V轉(zhuǎn)換為VOUT

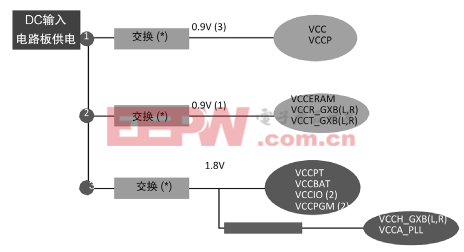

圖3 為Arria 10 GX推薦的電源樹

實現(xiàn)高密度布板,減小了雜散電感和電容。其次,較高的開 關(guān)頻率還支持更寬的控制環(huán)帶寬,也就意味著轉(zhuǎn)換器能夠更

迅速的響應(yīng)負(fù)載變化,結(jié)合使用更小的體電容,工作時也就

很少出現(xiàn)上沖或者下沖。由于體電容通常體積較大而且價格 昂貴,因此,減少體電容不但提高了瞬時響應(yīng)以保證無縫 工作,而且還節(jié)省了大量的電路板面積,降低了成本。圖1 說明了這一優(yōu)點,一個Altera Cyclone? V SoC設(shè)計使用了獨立的開關(guān)調(diào)節(jié)器,而相同的設(shè)計采用了Enpirion? PowerSoC。 Enpirion PowerSoC設(shè)計工作在較高的開關(guān)頻率下,利用獨特 的磁體和封裝集成技術(shù),使用了很少的電感和電容,實現(xiàn)了 密度極高的引腳布局,因此,器件的波紋很低,瞬時響應(yīng)很 快。用在Cyclone V SoC設(shè)計中,Enpirion PowerSoC將供電電 源引腳布局減小了22%,功耗降低了35%,不再需要5個較大 而且昂貴的鉭電容,體電容數(shù)量減少了一半。

在Cyclone V SoC開發(fā)套件上采用Enpirion PowerSoC解決方 案替代現(xiàn)有的供電電源解決方案,供電電源引腳布局減小了

22% (1a),功耗降低了35% (1b),去掉了昂貴的鉭電容,所需 的體電容減少了一半,從而減小了體積,降低了成本(1c)。

4 噪聲敏感輸入

雖然邏輯是FPGA架構(gòu)的主要構(gòu)件模塊,而FPG A還實現(xiàn)了很多其他的模塊,例如,鎖相環(huán)(PLL),用在FPGA內(nèi)部,將參考輸入時鐘與反 饋時鐘的上升沿對齊,

圖4 SmartVID實現(xiàn)

還有高速收發(fā)器,這是很多網(wǎng)絡(luò)、通信、存儲和其他 電子系統(tǒng)中不可或缺的組成。這些電路模塊對供電電源噪聲 非常敏感,因為噪聲會導(dǎo)致產(chǎn)生抖動,隨之帶來很高的誤碼 率(BER),降低了電路性能。FPGA及其最終應(yīng)用要求的邊 沿速率越來越高,使得越來越難以維持信號完整性。

結(jié)果,需要特殊考慮FPGA中這些模塊的供電電源,以減小電源軌噪聲。有時候,如果敏感的電源軌與系統(tǒng)中的另一穩(wěn)壓電源軌有相同的電壓要求,可以使用鐵氧體磁珠等價格便宜的小濾波器。但是,在很多情況下,要求使用輸出噪聲非常低的電源轉(zhuǎn)換器,才能獲得合適的穩(wěn)定的電壓。傳統(tǒng) 上,F(xiàn)PGA電路板設(shè)計人員簡單的使用低泄漏輸出線性調(diào)節(jié) 器(LDO),這通常會有較高的供電電源抑制比(PSRR),理論 上,不會產(chǎn)生開關(guān)噪聲。然而,線性調(diào)節(jié)器的效率非常低, 隨著收發(fā)器功耗需求的增長,系統(tǒng)總功耗預(yù)算越來越受限, 浪費的功率以及額外產(chǎn)生的熱量導(dǎo)致帶來更大的系統(tǒng)難題。 為解決這些難題, 敏感的FPG A電源軌可以使用很多 Enpirion PowerSoC解決方案,因為這些解決方案經(jīng)過設(shè)計, 實現(xiàn)了LDO的噪聲性能,同時維持了開關(guān)調(diào)節(jié)器的高效特 性。如圖2Stratix V GX FPGA電路板上高速信號張得很開的眼 圖所示,這是因為采用了Enpirion PowerSoC為收發(fā)器電源軌 供電。高頻硅片設(shè)計,即使是高頻工作時也能夠減小開關(guān)損 耗的高效的開關(guān)FET技術(shù),以及減小了雜散電感的獨特的封 裝結(jié)構(gòu),正是這些因素相結(jié)合,實現(xiàn)了低噪聲性能。(未完待續(xù))

評論