開放式FPGA可增加測試的靈活性

閉環測試:功放

在無線通信系統中,信號在發往天線之前需要用功放IC增加信號的強度。功放的性能規格通常是在特定的輸出功率電平點定義的。因此當功放工作在這個輸出功率電平時對它們進行測試就顯得非常重要。然而,功放的增益一般只是粗略的知道(比如±3dB),而且在器件工作范圍內是非線性的。你越接近最大輸出功率,增益就越低。基于這些理由,在開展任何性能測試之間你必須首先“調測”放大器的輸出。調測輸出經常被稱為功率電平調整或功率伺服調整。基本原理是調整放大器的輸入功率,直到你測得正確的輸出功率。

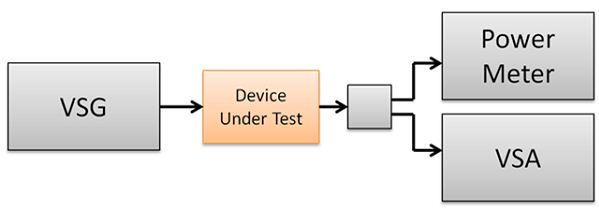

測量功放的傳統測試裝置見圖3所示。矢量信號發生器(VSG)產生一個激勵波形給待測設備。功率計確保待測設備輸出正確的功率電平。最后由矢量信號分析義(VSA)測量待測設備的性能——如誤差矢量幅度(EVM)或相鄰通道功率(ACP)。實際操作中需要針對各種中心頻率和功率電平重復這些測量。

圖3:用于測量功放輸出的傳統測試裝置包含有矢量信號發生器、矢量信號分析儀和功率計。

必須針對每個想要測試的中心頻率和功率電平調測功放的輸出功率。調測過程一般遵循以下這些步驟:

● 根據估計的待測設備增益選取一個起始的矢量信號發生器功率電平

● 設置矢量信號發生器的功率電平

● 等待矢量信號發生器穩定工作

● 等待待測設備穩定工作

● 用功率計進行測量

如果功率在正確的范圍內,退出。如果不在范圍內,計算新的矢量信號發生器功率電平,回到步驟2重新開始

整個調測過程可能要花幾百毫秒到幾秒的時間,具體取決于待測設備類型、要求的精度以及使用的儀器。調測過程完成后就可以用矢量信號分析儀開展性能測量了。

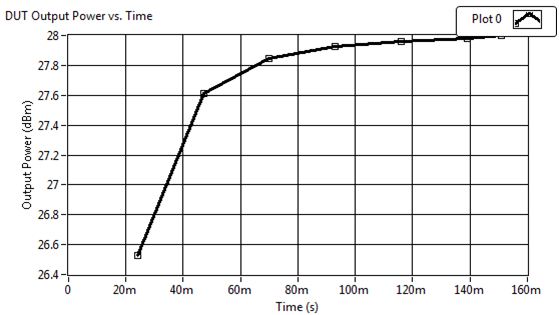

圖4顯示了使用傳統方法將待測設備樣品輸出調整到平均輸出功率為28dBm的過程。如果功率放大器的增益是線性的,并且符合數據手冊中規定的典型增益,那么矢量信號發生器產生的第一個點就將產生28dBm的輸出功率。然而放大器的實測輸出功率只有26.5dBm,這就表明了功放典型增益指標的不精確性。隨后調整矢量信號發生器的輸出功率,由矢量信號分析儀捕獲另外一個輸出功率點。這次平均功率是27.6dBm,從中可以看出放大器增益響應的壓縮過程。總之花了7步、大約150ms的時間才使放大器的輸出達到想要的功率值。在這個例子中,待測設備的穩定時間是每步10ms。但不同待測設備的穩定時間是不同的,它將顯著影響總的調測時間。

圖4:傳統的功放輸出調測方法表明功率電平是漸次增加的。

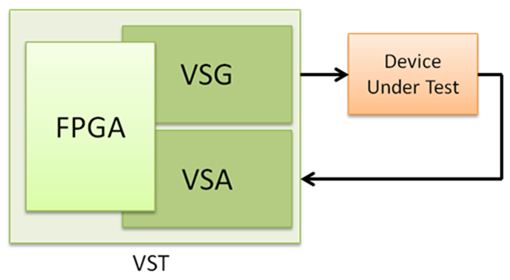

矢量信號收發器(VST)是將矢量信號發生器、矢量信號分析儀和FPGA整合在一起的一種儀器。這種組合可以讓你將功率調測算法轉移到硬件中實現。即使沒有圖5中的功率計,你通常也可以執行系統校準步驟將功率計精度轉嫁給矢量信號分析儀。

圖5:矢量信號收發器將信號發生器、信號分析儀和FPGA整合在一起。

調測功放輸出功率的步驟與傳統方法是類似的,只不過調測環路在開放式FPGA中執行。在FPGA中執行環路可以顯著縮短每次調整所需的時間。

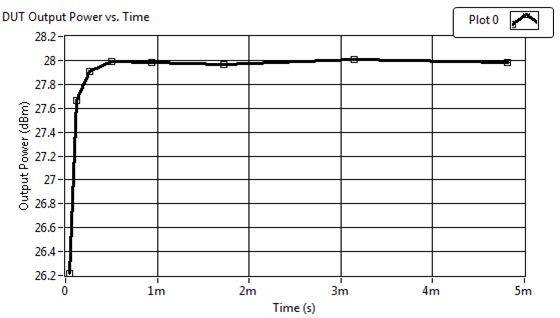

通過使用開放式FPGA和硬件并在FPGA上實現控制環路,調測待測設備輸出功率的時間將遠遠小于在主機電腦上執行控制環路的時間。對于本例中的待測設備來說,調測過程只用了5ms,而傳統方法需要150ms。需要注意的是,基于硬件的方法所需的步驟數比傳統方法多一步。但調測過程所需的總時間卻明顯減少。與圖4相比,圖6中的前幾個步驟完成得很快(平均時間較短),然后點的間隔越來越大,因為調測環路正在收斂。

圖6:使用基于硬件的調測方法后,功率電平上升的時間要短于傳統方法。

信號處理

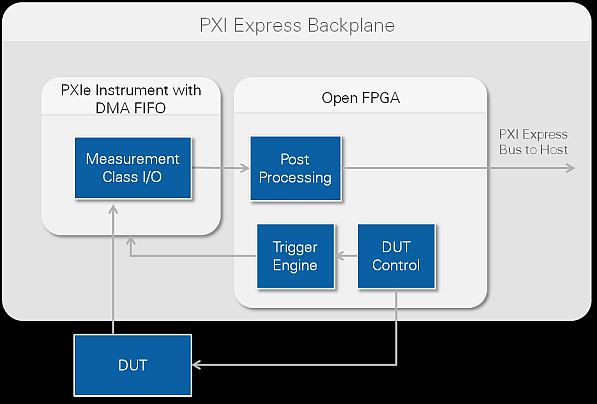

用戶可編程FPGA最有用的應用之一是在儀器上減少必須傳回主機進行后處理的數據量,從而釋放通信總線用于其它數據傳輸,同時減少CPU的負擔。用于這方面的常見方法包括復雜觸發、濾波、峰值檢測或對捕獲的數據集執行快速傅里葉變換(FFT)。

例如在圖7中你可以看到有4個待測設備需要并行測試的應用。模數轉換器(ADC)將樣本傳送給FPGA,但直到定制觸發器啟動捕獲命令后數據才被捕獲。在捕獲數據時,FPGA會實時平均測量結果,然后將它們連續進行記錄。然后在測量無雜散動態范圍(SFDR)、信噪比(SNR)和信號噪聲與失真比(SINAD)之前對記錄進行快速傅里葉變換。這些結果只是來自ADC的的輸入信號數據的一部分,接下來將通過直接存儲器訪問先入先出緩沖機制(DMA FIFO)上傳給主機。

評論