開放式FPGA可增加測試的靈活性

目前大多數儀器采用封閉式FPGA(現場可編程門陣列)和固定的固件實現儀器的功能。如果你曾見過示波器的拆解,你也許見過里面的FPGA。FPGA可以增加測試儀器的處理能力,如果你曾使用過儀器的開放式FPGA,你就會知道可以將自定義的測試功能編程進儀器中。

儀器供應商早就了解FPGA的好處,并且一直在充分發揮FPGA獨特的處理能力優勢來豐富的功能,比如:儀器

● 能夠在示波器上完成預觸發捕獲

● 能夠利用信號處理功能在矢量信號分析儀上產生I和Q數據

● 能夠在高速數字儀器上實時進行圖案發生和矢量比較

測試設備制造商現在開始向用戶開放FPGA以提供更多特殊應用的優化。為了幫助理解為何這是一個好的轉變,下面列出了在測試應用中使用FPGA的一些關鍵特性:

● 確定性,實時處理

● 真正并行的執行

● 可重配置

● 低延時

更進一步講,利用開放式FPGA可以實現哪些以前不能實現的功能呢?為了描述這些可能性,下面將介紹一些利用開放式FPGA的常見測試應用。

測試系統加速

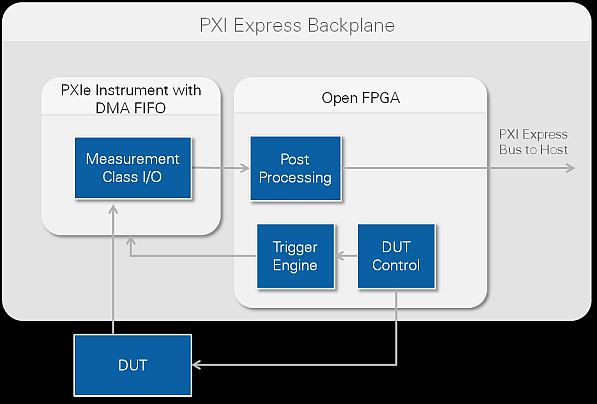

在大批量生產線的最終產品測試中,每一秒的測試時間都很寶貴。當產品測試速度與生產速度相匹配時,生產線的效率就是最高的。當兩者速度不匹配時,就必須采用創新的技術來縮短測試時間。傳統方法需要使用多臺分開的臺式儀器,它們通過以太網、USB或GPIB連接到一臺PC主機。這種測試的速度相對較慢,因為待測設備的控制、測量以及通過數據總線的處理是分開進行的。另外一種方法是使用開放式FPGA來加速這個過程,如圖1所示。

圖1:在測試儀器中,開放式FPGA可以增加諸如觸發和后處理等功能。

與使用外部通信總線不同,FPGA可以使用高速總線(如PXIe)連接儀器,并通過其配置端口(如I2C、SPI或另外的控制總線)連接待測設備(DUT)。這種應用中的FPGA可以控制待測設備,觸發其它儀器開始捕獲樣本,甚至將這些樣本處理成對主機來說有意義的結果。

低時延是加速這類應用的一個關鍵因素。FPGA沒有操作系統,但所有的邏輯都是用硬件實現,并且這些硬件工作的時鐘速率很高。這意味著響應只需花一個時鐘周期捕獲、一個時鐘周期處理和一個時鐘周期輸出結果。當時鐘速率為200MHz(時鐘周期為4ns)時,完整的響應時間只需12ns。由于FPGA的確定性特點,12ns的響應時間不是只有一次,而是每次都是。因此FPGA不僅可以避免與使用主機有關的延時,而且能夠最大限度地減小主機處理時的非確定性延時。

協議的處理

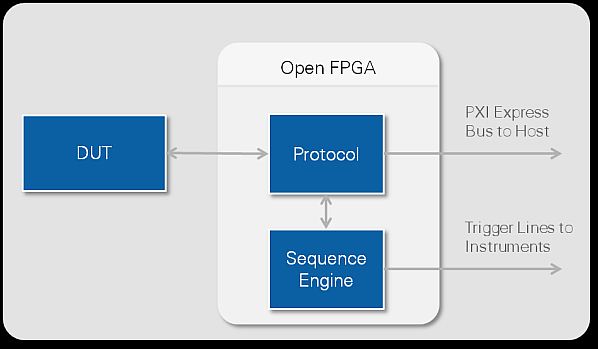

今天,并不是所有數字和MEMS設備都能用已知結果矢量進行測試。就拿脈沖密度麥克風(PDM)來說,如果給它一個激勵信號,你不能期望每次測試得到的比特流是完全相同的,這是因為PDM是模擬設備。為了從這些類型的待測設備獲得有意義的結果,在比較結果之前你首先需要用其特定的協議對數字流進行解碼。借助開放式FPGA,你可以在FPGA上配置你的測試系統來實現PDM協議,不必再傳至CPU進行解釋。進一步拓展這個概念,今天你可以配置這個FPGA實現PDM協議,明天你又可以重新配置同樣這個FPGA實現不同的協議,比如用于測試數字溫度傳感器、加速度計或MEMS設備的協議。

在圖2中,協議不是在CPU上實現,而是在FPGA上實現。正因為此,測試系統現在自身就可以支持快速握手腳本,適應精確等待周期等協議行為,并根據通信內容做出決策。這種方法不僅能讓你從待測設備接收更高層數據,比如在PDM麥克風場合中解碼的模擬數據,而且允許你用更高層命令編寫測試腳本。

圖2:FPGA可以用來處理協議,知曉總線使用的協議內容。

評論