信號完整性與電源完整性的仿真分析與設計

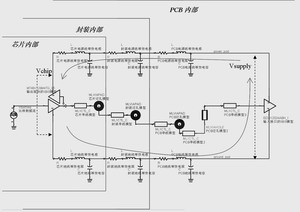

如圖3所示的電路仿真圖中包括了芯片、封裝及PCB板信號線互聯及電源互聯的等效模型。驅動電路和接收電路采用了IBIS模型(也可以用SPICE模型來替代)。利用該仿真電路,可以觀察到一個虛擬系統工作時任一點的信號波形或電源波動狀況。信號完整性通常關心的是時鐘信號的抖動以及信號波形的上升/下降/保持時間。將電路進行瞬態仿真后利用ADS2005A中內含的眼圖工具可自動統計出各抖動分量的值。

電源完整性通常關心的是工作器件所承受的實際電源電壓波動,即圖3中的Vchip。在實際分析中,系統集成設計的驗證者無法測到芯片內部的電源端口,所以無法觀測到芯片端口的電源波動和地彈噪聲,只能發現封裝外引腳處測得的電源與地是相當穩定的。但是,最終決定器件正常工作的電源應該是定義在芯片端口的,封裝端口的測量結果并不能反映出此時的電源完整性狀況。因此,需要芯片廠商提供封裝模型用來對芯片端口處的電源波動及地彈噪聲進行仿真。

圖3 簡化電路完整性仿真示意圖

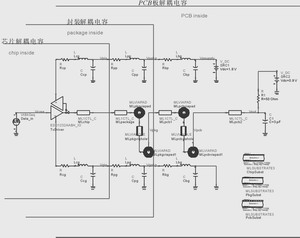

針對上述例子,進一步分別考慮在芯片內部、封裝內部以及PCB板加解耦電容,如圖4所示。用分別掃描解耦電容值的仿真方法來觀察解耦電容對電源完整性的影響。

圖4 仿真解耦電容效用的簡化原理圖

仿真結果表明,加在PCB板上以及封裝內的解耦電容并沒有明顯的作用,在芯片電路設計時增大I/O端口處的電容是最有效的方法。另外,還可以觀察到信號完整性與電源完整性的關聯性,改變不同解耦電容值后,不僅影響電源波動及地彈噪聲狀況,信號波形也發生了變化。對于對控制信號通路抖動要求較高的設計來說,還需要同時考慮電源完整性對抖動的影響。

系統完整性設計與分析

系統完整性設計與分析的必要性可以用一個簡單的例子來說明。圖2中的簡單電源傳遞網絡的仿真結果顯示,并不是在所有的頻點上都呈現出高阻抗。此時電源完整性與激勵信號的頻譜直接相關,如果在進行系統測試時的激勵信號避開3個諧振區,就不會呈現出高阻抗特性。因此,確定激勵信號的頻譜分布是分析與設計的前提。而激勵信號的頻譜分布根本上是由其數據內容所決定的,最終將歸結于協議的設計。

另一個更加實際的例子是目前電腦硬件接口由并行總線到串行總線的發展趨勢,如從PCI-X到PCI-E以及從ATA到SATA等。其中采用的信源及信道編碼技術,如時鐘擴頻、預加重技術等可以改善信號在特定環境中的傳輸性能。

結合信號完整性與電源完整性的定義,對參考端口的選取需要滿足可測性原則,這對于工程實現或調試有著直接的意義。但對于設計鏈中不同位置上的設計者,可測性的含義并不相同。對于芯片設計者來說,芯片之間的互聯結構可以設計特定測試芯片然后利用探針臺進行測試;但對于板級設計者來說,無法對手中的成品芯片甚至封裝中的互聯結構特性進行測試。當信號完整性的參考端口是定義在信道解碼器輸出處時,誤碼率的測試是非常重要的。比如,對擴頻時鐘的分析,只有在相關解調器的輸出處才能比較信號傳輸的質量,測量將會用到誤碼儀,而在無法測試的環境下只能依賴于誤碼率仿真等方法。

上述的幾種情況都要求在仿真分析中能夠集成考慮協議算法、電路結構以及互聯結構的影響,目前的仿真工具已經可以滿足該需求。在針對已有系統的分析中,由于系統完整性分析所包含的因素非常多,再加上協議建模需要相當大的工作量,因此,比較實用的方法是直接測量協議碼流(利用邏輯分析儀等儀器),并將之轉入到仿真平臺中作為電路的激勵。這種方法可以準確再現故障時的系統應用場景,有助于現場調試故障系統。解決方案如圖5所示。

圖5 結合測試建模的分析流程

該分析流程同樣也可以用在設計流程中,用測試的方法直接獲取待分析接口的協議數據,用于電路設計與版圖設計的前期驗證,但是,在硬件尚未實現時,將會用規范或之前的經驗值來與仿真結果比較。

結語

信號完整性與電源完整性系統分析與設計的根本需求來自于數據傳輸速率的快速增加,從而使得以前微秒(vs)量級的邊沿或保持時間減少到納秒(ns)甚至皮秒(ps)。如此高的帶寬需求使得僅考慮版圖級的解決方案已經很難滿足系統正常工作的需求。另外,集成電路的工藝發展使得集成度大大提高,芯片上電流密度的急速增加使這個問題更加嚴重。由此有必要從整個系統設計開始就考慮信號完整性與電源完整性的問題。

相應地,系統化仿真對于仿真工具也提出了新的挑戰,完整的仿真流程、方便的操作手段以及與測量的緊密結合才能夠快速有效地解決完整性問題。

評論