信號(hào)完整性與電源完整性的仿真分析與設(shè)計(jì)

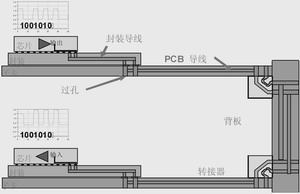

一個(gè)典型背板信號(hào)傳輸?shù)南到y(tǒng)示意圖如圖1所示。本文中系統(tǒng)一詞包含信號(hào)傳輸所需的所有相關(guān)硬件及軟件,包括芯片、封裝與PCB板的物理結(jié)構(gòu),電源及電源傳輸網(wǎng)絡(luò),所有相關(guān)電路實(shí)現(xiàn)以及信號(hào)通信所需的協(xié)議等。在設(shè)計(jì)時(shí),需要硬件提供可制作的支撐及電信號(hào)有源/無(wú)源互聯(lián)結(jié)構(gòu);需要軟件提供信號(hào)傳遞的傳輸協(xié)議以及數(shù)據(jù)內(nèi)容。但是,由于這些支撐與互聯(lián)結(jié)構(gòu)會(huì)對(duì)電信號(hào)的傳輸呈現(xiàn)出一定的頻率選擇性衰減,因此,會(huì)對(duì)信號(hào)及電源的完整性產(chǎn)生影響。同時(shí),在相同的傳輸環(huán)境下,不同傳輸協(xié)議及不同數(shù)據(jù)內(nèi)容的表達(dá)方式具有不同的適應(yīng)能力,因此,需要進(jìn)一步根據(jù)實(shí)際的傳輸環(huán)境來(lái)選擇或優(yōu)化可行的傳輸協(xié)議及數(shù)據(jù)內(nèi)容表達(dá)方式。

圖1 背板信號(hào)傳輸?shù)南到y(tǒng)示意圖

版圖完整性問(wèn)題、分析與設(shè)計(jì)

上述背板系統(tǒng)中的硬件支撐及無(wú)源互聯(lián)結(jié)構(gòu)基本上都在一種層疊平板結(jié)構(gòu)上實(shí)現(xiàn)。這種層疊平板結(jié)構(gòu)可以由3類元素組成:正片結(jié)構(gòu)、負(fù)片結(jié)構(gòu)及通孔。正片結(jié)構(gòu)有時(shí)也被稱為信號(hào)層,該層上的走線大多為不同邏輯連接的信號(hào)線或離散的電源線,在制版光刻中所有的走線都會(huì)以相同圖形的方式出現(xiàn);負(fù)片結(jié)構(gòu)有時(shí)也被稱為平面層(細(xì)分為電源平面層和地平面層),該層上基本是相同邏輯的一個(gè)或少數(shù)幾個(gè)連接(通常是電源連接或地連接),用大面積敷銅的方式實(shí)現(xiàn),在光刻工藝中用相反圖形來(lái)表示;通孔用來(lái)進(jìn)行不同層之間的物理連接。目前的制造工藝中,芯片、封裝以及PCB板大多都是在類似結(jié)構(gòu)上實(shí)現(xiàn)的。

版圖完整性設(shè)計(jì)的目標(biāo)在于為系統(tǒng)提供足夠好的信號(hào)通路以及電源傳遞網(wǎng)絡(luò)。電流密度分布對(duì)于版圖完整性設(shè)計(jì)與分析有著重要的意義,這是因?yàn)殡娏髅芏瓤梢灾庇^地顯示信號(hào)的寄生耦合位置以及強(qiáng)度,從而幫助版圖調(diào)試者有針對(duì)性地采取耦合或解耦方案。

對(duì)于信號(hào)完整性來(lái)說(shuō),首要任務(wù)是保證信號(hào)通路在一定負(fù)載情況下呈現(xiàn)良好的匹配狀況,同時(shí)避免寄生耦合改變已設(shè)計(jì)好的匹配狀況。利用電磁場(chǎng)仿真不但可以準(zhǔn)確地計(jì)算實(shí)際版圖結(jié)構(gòu)中信號(hào)通路的匹配狀況,也可以計(jì)算信號(hào)通路周圍結(jié)構(gòu)帶來(lái)的寄生耦合(如果周圍是信號(hào)線則通常被稱為串?dāng)_),其強(qiáng)度可以直接表示為周圍走線或平面上感應(yīng)所產(chǎn)生的電流密度,從而有助于優(yōu)化版圖結(jié)構(gòu)。除改變線距外,改變周圍其它電磁回路環(huán)境也會(huì)導(dǎo)致信號(hào)傳輸及串?dāng)_狀況的變化。比如,利用層與層之間的屏蔽可以改善原本放在頂層的走線信號(hào)傳輸或串?dāng)_性能。

對(duì)于電源完整性來(lái)說(shuō),增加電源與地之間的容性耦合可以濾除電源中的交流波動(dòng)。在實(shí)際應(yīng)用中,往往采取加解耦電容的方法。電流密度的動(dòng)態(tài)顯示可以幫助設(shè)計(jì)者直觀了解到電源網(wǎng)絡(luò)中產(chǎn)生振蕩現(xiàn)象的原因。從而幫助設(shè)計(jì)者確定加解耦電容的最佳位置。

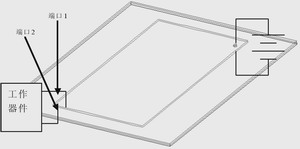

圖2中模擬了一種簡(jiǎn)單的電源傳遞網(wǎng)絡(luò),電源平面和地平面是規(guī)整的矩形,這有助于定性地驗(yàn)證電磁場(chǎng)仿真結(jié)果。工作器件與供電電源分別連接在矩形的兩個(gè)對(duì)角上。假設(shè)工作器件對(duì)于該供電網(wǎng)絡(luò)的阻抗為20。利用電磁場(chǎng)仿真可以觀察電流從端口1流入,經(jīng)過(guò)該電源傳遞網(wǎng)絡(luò)再?gòu)亩丝?流出的損耗狀況。

圖2 簡(jiǎn)單的電源傳遞網(wǎng)絡(luò)仿真

仿真中用一個(gè)過(guò)孔在電源連接處短接電源平面與地平面來(lái)模擬接上電源的情況(假設(shè)電源內(nèi)阻很小可以忽略)。由仿真結(jié)果可知此電源傳遞網(wǎng)絡(luò)在1GHz頻段內(nèi)出現(xiàn)了3個(gè)主要諧振區(qū)域,分別在200MHz、500MHz以及1GHz附近。諧振區(qū)域的存在對(duì)于電源完整性會(huì)產(chǎn)生一定的影響:如果工作器件(以典型的CMOS器件為例)在諧振頻點(diǎn)上工作,會(huì)產(chǎn)生同樣頻點(diǎn)的電源電流需求,但是,由于存在諧振,從供電電源端到器件電源輸入端就會(huì)產(chǎn)生明顯的壓降,從而使工作器件上實(shí)際的工作電壓達(dá)不到預(yù)期值,導(dǎo)致器件性能惡化,甚至無(wú)法正常工作。解決上述問(wèn)題的常用方法是加解耦電容,使電源網(wǎng)絡(luò)的諧振區(qū)遠(yuǎn)離器件的工作頻率。通過(guò)電流密度分布的顯示可以了解振蕩原因,從而采取針對(duì)性方法。對(duì)上述電源網(wǎng)絡(luò)來(lái)說(shuō),可以加一個(gè)過(guò)孔來(lái)模擬解耦電容,并通過(guò)改變過(guò)孔的位置來(lái)觀察諧振模式及諧振點(diǎn)的變化,從而找到放置解耦電容的最佳位置。

電路完整性設(shè)計(jì)與分析

從TTL、GTL 到HSTL、SSTL以及 LVDS,目前芯片接口物理標(biāo)準(zhǔn)的演變反映了集成電路工藝的不斷進(jìn)步,同時(shí)也反映了高速信號(hào)傳輸要求的不斷提高。從版圖完整性的分析過(guò)程可知,只有結(jié)合了互聯(lián)結(jié)構(gòu)兩端負(fù)載特性的仿真結(jié)果才具有實(shí)際意義,而負(fù)載特性是由其連接的電路特性所決定的,因此,在完整性設(shè)計(jì)中,了解這些接口標(biāo)準(zhǔn)是非常必要的。隨著傳輸速率的不斷增加,翻轉(zhuǎn)速率控制電路、驅(qū)動(dòng)負(fù)載控制電路被廣泛使用,它們?yōu)橥暾栽O(shè)計(jì)者提供了更多的優(yōu)化空間。在具體的完整性分析中,電路設(shè)計(jì)者需要考慮這些控制的實(shí)際實(shí)現(xiàn)方式,因?yàn)樗鼈儠?huì)影響到電路的負(fù)載特性以及波形性能。另外,還需考慮芯片上解耦電容的實(shí)現(xiàn)。

評(píng)論