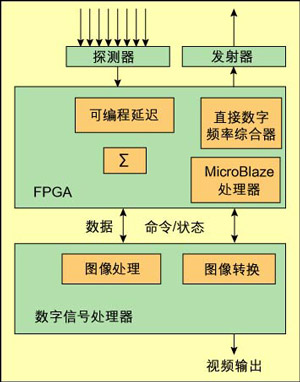

用DSP和FPGA構(gòu)成多普勒測量系統(tǒng)

DSP讀取和存儲FPGA執(zhí)行操作的結(jié)果。一旦完成一系列掃描,處理器就可以構(gòu)建出一幅針對掃描區(qū)域的數(shù)字圖像。可以為不同的速度分配不同的顏色(按照線性、對數(shù)或任何其他比例),并將數(shù)字圖像轉(zhuǎn)換成視頻圖像,在圖形終端上實時顯示或記錄下來留待以后回放。利用眾多可以得到的軟件或工具包中的一個,還可以在處理器中輕松實現(xiàn)到JPEG或其他視頻格式的轉(zhuǎn)換, 還可以采用其他系統(tǒng)分割進行實驗。如果實時視頻處理和存儲占用了處理器過多帶寬,可以將算法的一部分(比如掃描數(shù)據(jù)的預處理)放在FPGA中來執(zhí)行。

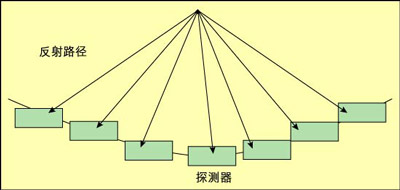

測量過程的另一個重要部分是確定目標的質(zhì)量。可以通過測量從焦點返回探測器的能量大小來實現(xiàn)這一功能。返回的能量越多,則目標越大(一般而言)。當測量的目標具有固定連貫性時(如在管道中流動的油或其他液體),這種測量效果特別好,但當系統(tǒng)中存在各種不同質(zhì)量或反射時,測量就很困難了。

顯然,對被測系統(tǒng)多些了解可以為測量過程提供一些線索。通過存儲與返回信號的幅度相對應的數(shù)字值,可以為FPGA協(xié)處理器增加能量測量功能。該值也是經(jīng)過了FPGA的延遲。

作為選擇,JPEG處理可以作為一項獨立的功能通過FPGA來執(zhí)行,從而使處理器留出更多時間進行數(shù)據(jù)預處理器。有許多選項可供選擇,但提供一種能夠快速實現(xiàn)不同分割的易用平臺才是至為重要的。

類似的以協(xié)處理為本的應用可以從硬件開發(fā)平臺的使用中獲得好處。利用硬件平臺可以讓您輕松實驗各種系統(tǒng)和算法分割--將一些功能在FPGA 中實現(xiàn),而另一些功能放在DSP中。DSP應用程序一般很難用軟件進行仿真,因此快速創(chuàng)建硬件/固件/軟件平臺的能力可以極大地縮短開發(fā)時間。使用賽靈思工具套件中的協(xié)仿真工具,通過The MathWorks Simulink和目標硬件進行開發(fā),是一種可以大大縮短設計時間的技巧。

圖3:示例系統(tǒng)框圖。

Avnet DSP協(xié)處理器設計套件

Avnet DSP協(xié)處理設計套件是針對以DSP為導向、同時需要使用FPGA和DSP的廣泛應用開發(fā)而設計的。套件配有兩塊主電路板。Virtex-4評估板(如圖4所示)配有 Xilinx Virtex-4 SX-FF668 FPGA、平臺閃速配置PROM、擴展連接器、CypressCY7C68013USB2.0 控制器、國家半導體的DP83847 10/100 以太網(wǎng)端口、128x64 OSRAM 圖形顯示器、8MB閃存、32MB DDR SDRAM 以及各種用戶開關(guān)和LED。第二塊電路板是 TI DSP 適配器模塊(如圖5所示),用于在Virtex-4 電路板和各種 TI DSP評估板之間起接口作用。可以從 Avnet公司購買TI電路板,完成開發(fā)平臺的構(gòu)建。 本文引用地址:http://www.104case.com/article/201702/338454.htm

評論