關于測量中的建立時間和保持時間的理解

建立時間與保持時間

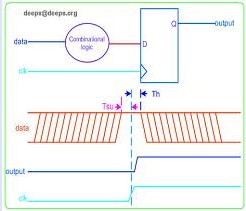

本文引用地址:http://www.104case.com/article/201701/338025.htm建立時間(Tsu:set up time)是指在時鐘沿到來之前數據從不穩定到穩定所需的時間,如果建立的時間不滿足要求那么數據將不能在這個時鐘上升沿被穩定的打入觸發器;保持時間(Th:hold time)是指數據穩定后保持的時間,如果保持時間不滿足要求那么數據同樣也不能被穩定的打入觸發器。建立與保持時間的簡單示意圖如下圖1所示。

圖1 保持時間與建立時間的示意圖

在FPGA設計的同一個模塊中常常是包含組合邏輯與時序邏輯,為了保證在這些邏輯的接口處數據能穩定的被處理,那么對建立時間與保持時間建立清晰的概念非常重要。下面在認識了建立時間與保持時間的概念上思考如下的問題。舉一個常見的例子。

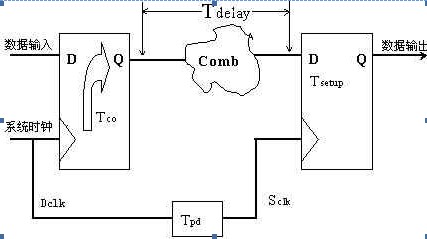

圖2 同步設計中的一個基本模型

圖2為統一采用一個時鐘的同步設計中一個基本的模型。圖中Tco是觸發器的數據輸出的延時;Tdelay是組合邏輯的延時;Tsetup是觸發器的建立時間;Tpd為時鐘的延時。如果第一個觸發器D1建立時間最大為T1max,最小為T1min,組合邏輯的延時最大為T2max,最小為T2min。問第二個觸發器D2立時間T3與保持時間T4應該滿足什么條件,或者是知道了T3與T4那么能容許的最大時鐘周期是多少。這個問題是在設計中必須考慮的問題,只有弄清了這個問題才能保證所設計的組合邏輯的延時是否滿足了要求。

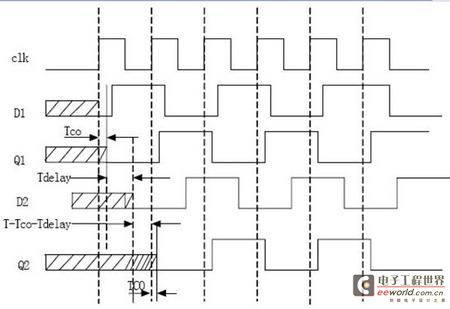

下面通過時序圖來分析:設第一個觸發器的輸入為D1,輸出為Q1,第二個觸發器的輸入為D2,輸出為Q2;

時鐘統一在上升沿進行采樣,為了便于分析我們討論兩種情況即第一:假設時鐘的延時Tpd為零,其實這種情況在FPGA設計中是常常滿足的,由于在FPGA 設計中一般是采用統一的系統時鐘,也就是利用從全局時鐘管腳輸入的時鐘,這樣在內部時鐘的延時完全可以忽略不計。這種情況下不必考慮保持時間,因為每個數據都是保持一個時鐘節拍同時又有線路的延時,也就是都是基于CLOCK的延遲遠小于數據的延遲基礎上,所以保持時間都能滿足要求,重點是要關心建立時間,此時如果D2的建立時間滿足要求那么時序圖應該如圖3所示。

從圖中可以看出如果:

T-Tco-Tdelay>T3

即: Tdelay< T-Tco-T3

那么就滿足了建立時間的要求,其中T為時鐘的周期,這種情況下第二個觸發器就能在第二個時鐘的升沿就能穩定的采到D2,時序圖如圖3所示。

圖3 符合要求的時序圖

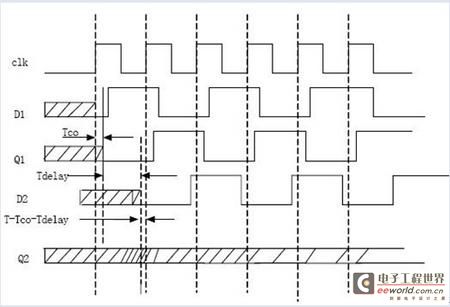

如果組合邏輯的延時過大使得

T-Tco-Tdelay 那么將不滿足要求,第二個觸發器就在第二個時鐘的升沿將采到的是一個不定態,如圖4所示。那么電路將不能正常的工作。

技術專區

評論