多通道高帶寬同步采集系統

示波器作為基礎性的通用時域儀器,廣泛應用于電子相關領域的測量。一般示波器最多配備4個通道。而一些應用需要測試的通道數可能大于4個。例如多通道的高速串行總線(PCI Express x8,x16,x32)、DP-QPSK、天線陣列、相控陣雷達、衛星導航裝置等等。這些應用有時需要在時域上采集多個信號,這就需要多通道且高帶寬、高采樣率的時域儀器。

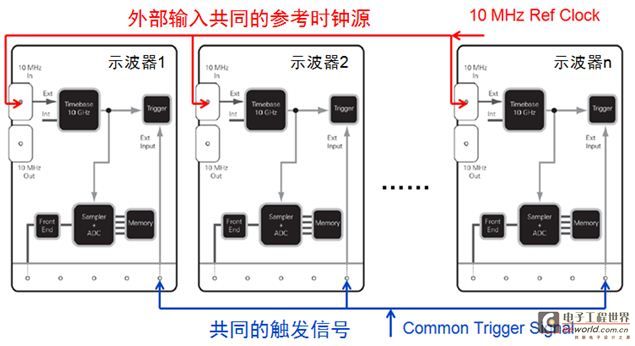

本文引用地址:http://www.104case.com/article/201701/337851.htm為了實現更多采集通道,傳統的做法是將多臺示波器同步起來使用。所謂示波器同步,就是每臺示波器的參考時鐘同源(相參)、觸發時刻一致(采集時刻一致)。多臺示波器同步方法如圖 1,一個外部的時鐘源輸出到每臺示波器,并且每臺示波器由同一個信號進行觸發。

圖 1同步多臺示波器連接示意圖

美國力科公司針對這類應用,推出了解決方案:多通道、高帶寬、模塊化示波器系統LabMaster,外觀如圖 2 所示。采集通道模擬帶寬可達45GHz,采樣率可達120G Sample/s,通道數則可以達到20個。

圖 2 示波器系統LabMaster (左側為20通道,右側為8通道)

多通道采集系統很大一部分應用的目的是測試各信號之間的時序或相位差,或者要求采集系統不影響信號之間的相位和時序關系。這要求采集系統具有比較高的同步精度,特別是對于一些高頻、高速信號的測試,同步精度要求達到ps量級。可以按下面方法來評估采集系統的同步精度:將兩個相位相同的正弦信號同時輸入到采集系統任意兩個通道,經過采集后,測量兩個信號的相位差,這個相位差就是這兩個采集通道之間的同步精度,或者稱為時序偏斜(skew)、相位誤差。

本文主要從同步精度的角度來對比傳統的多臺示波器同步方式和LabMaster示波器系統,

二.同步精度分析

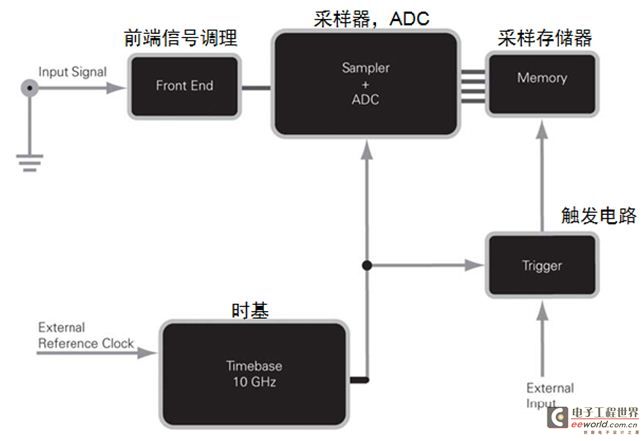

為了便于討論示波器的同步精度,先來分析一下示波器采集電路的結構。單臺示波器采集電路框圖如圖 3。信號先經過前端調理后,由模數轉換器(ADC)進行量化。ADC由一個10GHz時鐘驅動,稱為時基(Timebase)時鐘,產生時基時鐘的電路稱為時基電路。ADC量化的數據存入采集存儲器(Memory)中,這是一個先入先出(FIFO)存儲器,受觸發電路控制。如果沒有觸發,采集存儲器的內容不斷被更新。如果觸發條件到來,觸發電路控制存儲器停止更新,并把此時刻保存的數據送去顯示和處理。隨后恢復更新,觸發電路等待下一次觸發條件。

圖 3示波器采集電路框圖

一臺4通道的示波器,包含4套前端信號調理電路、ADC和采集存儲器,它們共用一個時基電路和一個觸發電路。

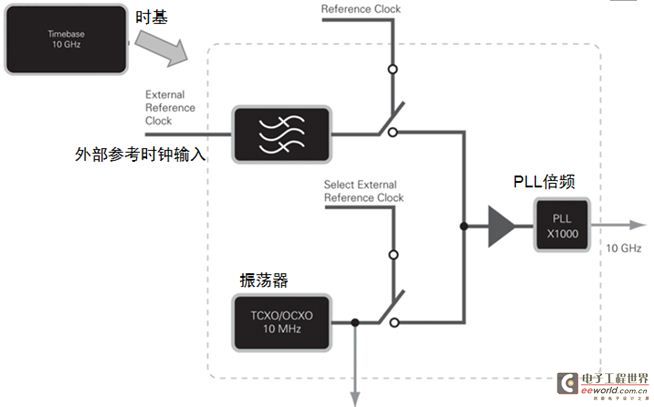

再將時基電路的結構細化,如圖 4。10GHz時基時鐘由一個10MHz的低頻時鐘通過PLL倍頻1000倍得到,這個低頻時鐘稱為參考時鐘,它可以由示波器內部的晶體振蕩器(TCXO/OCXO)產生,也可以由外部輸入(External Reference Clock)。內部產生的10MHz也可以輸出給其他示波器。示波器一般都有參考時鐘的輸入和輸出接口,輸入的時鐘只能是低頻,在內部還要經過倍頻。

圖 4示波器采樣系統的時鐘

把多臺示波器同步起來使用時,示波器引入的時序偏斜主要包含以下部分:

時鐘的偏斜和抖動

觸發信號偏斜和抖動

通道延遲

1)時鐘的偏斜和抖動

時基時鐘經過分布網絡傳輸到各通道ADC的延遲難免有差異,而每個通道的ADC都在時基時鐘上升沿50%時刻進行采樣和量化,這樣各通道ADC采樣時刻有偏差。這種偏差是固有的、靜態的,可以通過校準的方式消除。但時鐘難以避免抖動(jitter),抖動也會導致各通道采樣時刻有偏差,并且這種抖動是動態的、時變的,無法消除。只能選擇時基時鐘抖動小的示波器。高帶寬數字示波器一般都有一個規格指標稱為抖動噪底(Jitter Noise Floor),該指標是時鐘抖動、垂直噪聲等示波器自身引入“干擾”在最終測試結果上的形式的反映。例如力科四通道示波器WaveMaster 8Zi-A的抖動噪底為125fs。

單臺四通道示波器的時基時鐘抖動可能很小。但用同步方式實現多通道時,時鐘抖動就很難控制在比較小的水平了。多臺示波器同步需要一個額外的信號源輸出10MHz時鐘分配到每個示波器的參考時鐘輸入接口,如圖 1中的紅線所示,也可以把一臺示波器的參考時鐘輸出給其他各臺示波器。無論哪種參考時鐘產生方式,都需要一個時鐘分配網絡,這往往是測試系統集成者定制的,難以保證高穩定度,容易受到噪聲的影響。而低頻的參考時鐘更容易受噪聲影響。

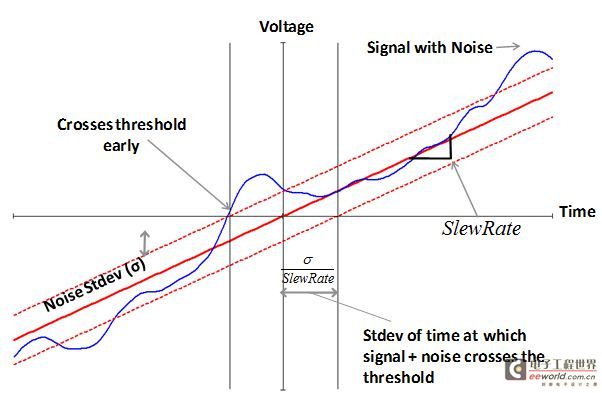

為什么低頻時鐘對噪聲更敏感呢?低頻意味著信號擺率(slew rate)較小。信號擺率用來描述信號邊沿變化的快慢程度,數值上SlewRate=dv/dt,可以等同于邊沿的斜率。相同幅度的時鐘信號,頻率低的邊沿擺率小。因為噪聲的影響,時鐘上升沿50%電平的發生時刻可能提前或延后,從而使幅度噪聲轉換為時間抖動,如圖5,轉換關系為dt=dv÷SlewRate,這意味參考時鐘擺率越小,同樣幅度噪聲引起的抖動更大。

圖5幅度噪聲轉換為時間抖動

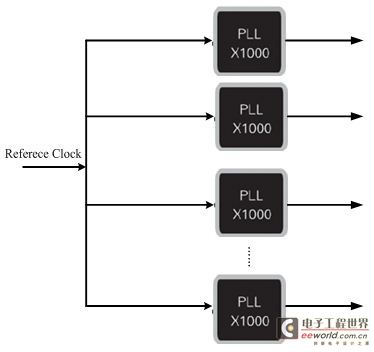

因為低頻參考時鐘進入示波器后還需要經過PLL倍頻才能作為ADC的采樣時鐘,所以多臺示波器同步方式的時鐘結構是如圖6,一個參考時鐘同時輸入到多個PLL,

圖6多臺示波器同步方案的時鐘拓撲結構

一方面PLL倍頻會加重時鐘的抖動。另一方面由于多個PLL輸入并聯在一起,它們之間相互干擾,也會加重時鐘抖動。

總結一下多臺示波器同步方式的時鐘抖動性能:外部輸入的低頻參考時鐘容易受干擾,并且多個PLL倍頻會加重時基時鐘的抖動,最終影響各個通道之間的同步精度。

評論