FPGA中定時循環啟動開銷測試

1. 背景及目的

在FPGA代碼中,會遇到將定時循環嵌入非定時循環的情況,此時定時循環將反復啟動和停止。這個定時循環的時間開銷如何,需要測試驗證。

定時循環的時間開銷應包含兩個方面:1.定時循環的啟動開銷,2.定時循環的運行開銷。

對于第1點,目前沒有找到FPGA的具體說明信息,而且這個時間開銷應該和具體的時鐘配置相關。

對于第2點,FPGA編譯保障了每遍運行時間嚴格按照指定時鐘周期運行。

所以,可以編寫簡單程序測試FPGA定時循環的啟動時間開銷。

2. 測試方法

軟硬件環境:LabVIEW 2011,LabVIEW FPGA 2011

NI PXI-7851

測試配置及代碼:

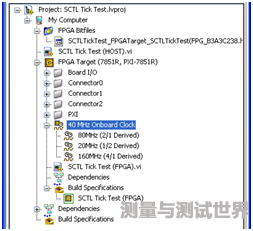

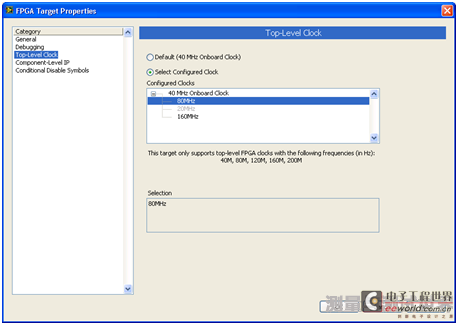

1.FPGA Target下新建多個時鐘

2.FPGA Target的top-level clock配置為80MHz時鐘

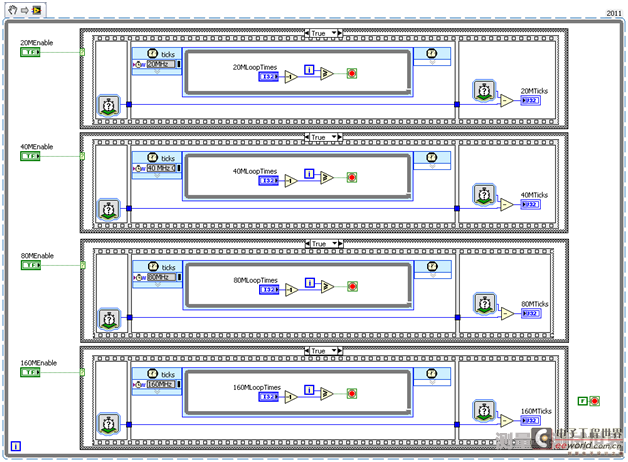

3.FPGA代碼中對不同時鐘運行指定次數進行計時

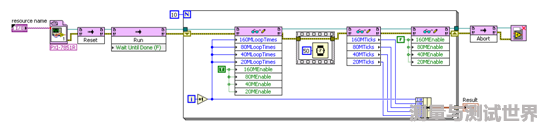

4.Host端指定循環次數,并讀取每次的計時結果

3. 測試結果

由于Top-Level clock是80MHz,所以所有計時器的1個Tick代表的是80MHz時鐘的1周期,

在160M時鐘下,定時循環的啟動時間開銷約10個Tick,運行時間是每遍循環0.5個Tick;

在80M時鐘下,定時循環的啟動時間開銷約1個Tick,運行時間是每遍循環1個Tick;

在40M時鐘下,定時循環的啟動時間開銷約為28個Tick,運行時間是每遍循環2個Tick;

在20M時鐘下,定時循環的啟動時間開銷約為48個Tick,運行時間是每遍循環4個Tick。

結果表明:

與Top-Level Clock 相同時鐘驅動的定時循環的啟動時間開銷大大小于其他時鐘下的定時循環。

在非Top-Level Clock情況下,定時循環的時鐘頻率越低,啟動時間越長。

4. 結論

在FPGA代碼中,

盡量避免循環的嵌套。盡量讓最外層循環為定時循環。

定時循環的啟動有時間開銷。如果在非定時循環中反復運行定時循環,需要考慮定時循環的啟動開銷。

盡量讓非定時循環中的定時循環工作在Top-Level Clock下,此時的啟動開銷為1個Tick。

評論