《Cortex-M0權威指南》之體系結構---系統模型

Cortex-M0體系結構包括:系統模型、存儲器映射、異常中斷。這篇文章主要講解Cortex-M0的系統模型。

本文引用地址:http://www.104case.com/article/201612/341938.htm操作模式和狀態

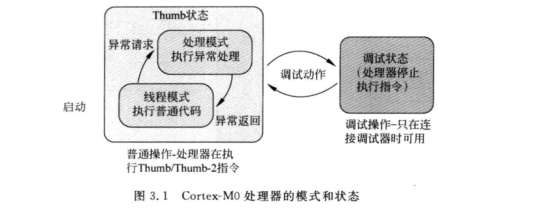

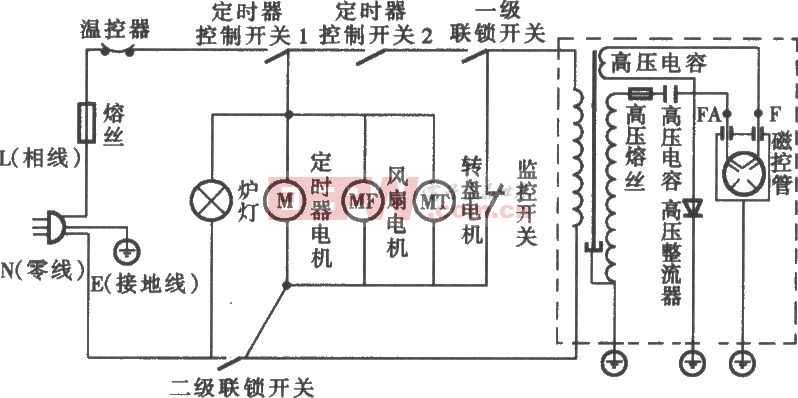

如上圖所示,Cortex-M0包括兩種操作模式和兩種狀態

處理模式

線程模式

調試狀態

處理器啟動后處于Thumb狀態,在這種狀態下,處理器可以處于線程模式和處理模式,線程模式時執行普通代碼,處理模式時執行異常處理。線程模式和處理模式的系統模型幾乎一模一樣,唯一的不同在于線程模式通過配置CONTROL特殊寄存器,可以使用進程指針。

調試狀態僅用于調試操作,暫停處理器內核后,執行不會再執行。在這種狀態下,調試器可以讀取甚至改變內核寄存器的值。

處理器上電后默認處于Thumb狀態的線程模式,執行普通代碼。

寄存器和特殊寄存器

數據的解析和控制器的處理過程中,需要處理器內核寄存器的參與。如果需要處理控制器中的數據,這些數據需要先加載到處理器內核的寄存器(寄存器組中的摸個),處理完成后,如果有需必要,它們還會被送到存儲器中,這種方式被稱為“加載-存儲架構”(load-store architecture)。

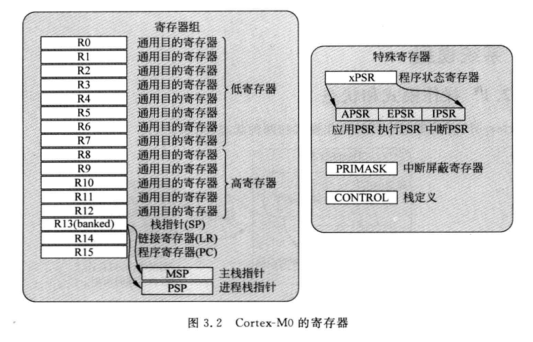

Cortex-M0有13個32位通用寄存器R0-R12,以及多個特殊寄存器。

寄存器組包含16個32位寄存器,其中13個時通用的,其余三個具有特殊用途。

R0-R12 通用寄存器

R0-R12為32位通用寄存器,由于16位thumb指令集在空間上的限制,許多Thumb指令只能操作R0-R7,它們被稱為低寄存器,而想MOV之類的一些指令則可以使用全部的寄存器。R0-R12寄存器的初始化值未定義。

R13,棧指針(SP)

R13為棧指針,對棧空間進行存取操作(通過PUSH和POP指令),Cortex-M0在不同的物理地址上有兩個棧指針,一個為主棧指針(MSP),也被稱為SP_main,一個指針稱為進程棧指針(PSP),也為稱為SP_process,只能用在線程模式。可以通過CONTROL寄存器,選擇使用那個棧指針。

在ARM處理器中,由于寄存器是32位的,所以PUSH和POP指令永遠是32位操作,而且存取地址是32位字對齊(32位對齊)。在處理器上電過程中,中斷向量表的頭4字節會被去除(中斷向量表在0x000000000地址),然后填充到MSP,作為MSP的初始值,PSP的初始值為定義。

一般使用操作系統是PSP進程棧指針才會被使用,這是因為操作系統內核的棧空間和線程級的應用程序的棧空間是相互獨立的。

R14,鏈接寄存器(LR)

R14為鏈接寄存器,用于存儲子程序或者函數調用的返回地址。子程序或者函數執行完畢,存儲在LR中的返回地址將被裝在到程序計數器PC中,以便調用程序可以繼續執行。當發生異常中斷時,LR會提供一個特定值,用于中斷返回機制。

盡管Cortex-M0處理器的函數返回地址始終時偶數(最低位為0,因為最小的指令都是16位的),LR的0位時可讀寫的。為了指明當前處于thumb狀態,一些指令需要函數地址最低位為1。

R15,程序計數器(PC)

R15為程序計數器,為可讀寫。讀操作返回當前正在執行的指令加上4(這是由流水線的特性決定的),而寫入R15會導致程序跳轉執行,這和函數調用不同,鏈接寄存器不會更新。

Cortex-M0處理器指令是16位對齊的,所以PC寄存器的最低位必須始終為0.不過在使用跳轉指令BX或者BLX執行跳轉執行時,PC的最低位應該被置1,以表明目標分支處于thumb程序區域。如果試圖切換到Cortex-M0未知的ARM狀態,錯誤異常中斷會被觸發。

xPSR,組合程序狀態寄存器

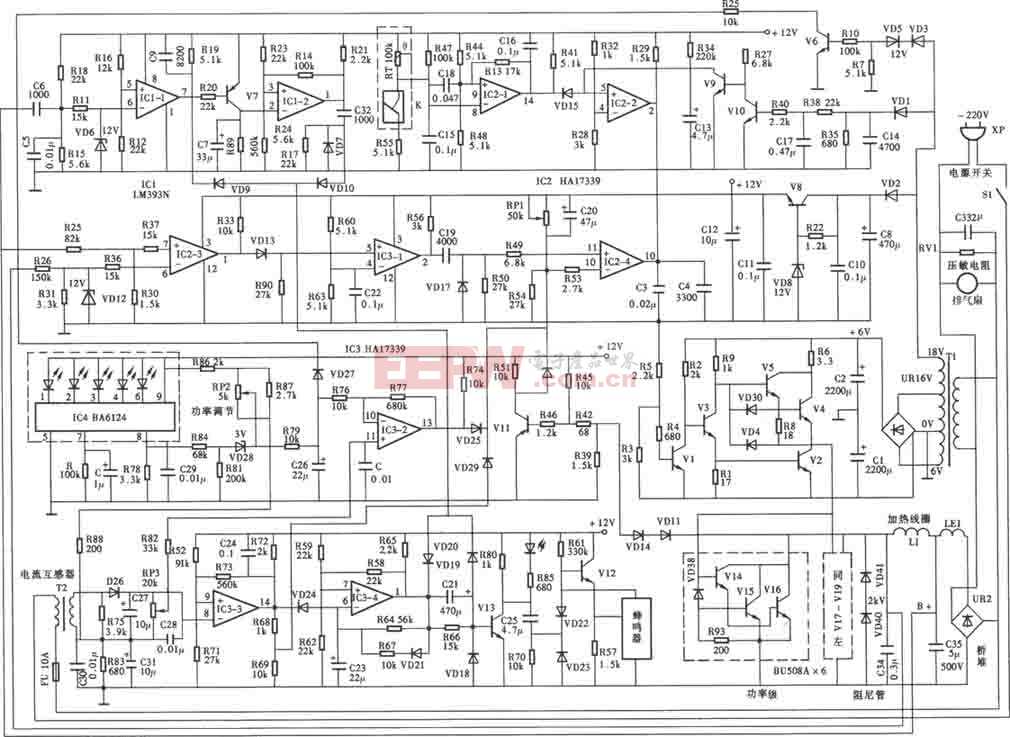

xPSR寄存器

xPSR寄存器

組合程序狀態寄存器提供了程序執行信息和ALU(算數邏輯單元)標志,改寄存器由三個程序狀態寄存器(PSR)組成,如上圖:

應用程序狀態寄存器(APSR)

中斷程序狀態寄存器(IPSR)

執行程序狀態寄存器(EPSR)

應用程序狀態寄存器

APSR包含了ALU算數邏輯單元標志,位于xPSR最高4位,一般用于控制程序跳轉:

N表示負號標志

Z表示零標志

C表示進位或借位標志

V表示溢出標志

中斷程序狀態寄存器

IPSR包含了當前正在執行的中斷服務程序(ISR)編號,Cortex-M0的每個異常中斷都會由一個特定的中斷編號(表示中斷類型)。這對調試時識別當前的中斷非常有用,而且在多個中斷共用一個中斷處理的情況下,可以看出放生的時哪個中斷。

執行程序狀態寄存器

EPSR包含了T位,該位用來表示當前是否處于Thumb狀態。由于Cortex-M0處理器只支持Thumb狀態,所以T位一般為1.清除該位(置零)后,執行嚇一跳置零會觸發硬件異常中斷。

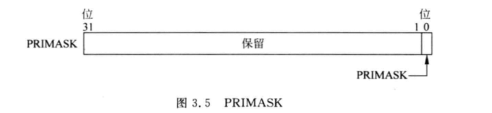

PRIMASK,中斷屏蔽特殊寄存器

PRIMASK僅有一位位寬,置位后,除了不可屏蔽中斷(NMI)和硬件錯誤異常外的其他中斷都會被屏蔽。實際上,此時當前中斷優先級被置為0,也就是最高等級。

要訪問PRIMASK寄存器,可以通過特殊寄存器操作置零(MSR和MRS),也可以使用“改變處理器狀態”置零(CPS)。在處理器對事件敏感的應用時,需要操作PRIMASK寄存器。

CONTROL,特殊寄存器

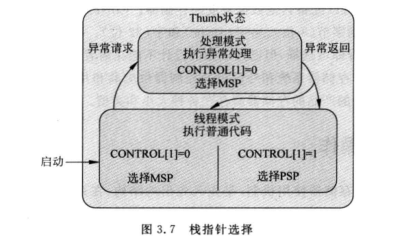

前面已經提到,Cortex-M0處理器具有兩個棧指針。處理器模式決定了使用的棧指針,而處理器模式以來與CONTROL寄存器的配置。

復位以后,系統默認使用主棧指針,在線程模式下,通過配置CONTROL寄存器的第一位置1,處理器可以切換至使用進程棧指針(前提是當前不是處在異常中斷處理中)。在處理異常中斷時(運行在處理模式下),系統只能使用主棧指針,CONTROL寄存器讀出的值為0。要改變CONTROL寄存器的值,應該在線程模式下進行操作,或者借助異常中斷進入和返回機制。

為了兼容Cortex-M3,CONTROL寄存器的0位保留。在Cortex-M3中,第0位用于將處理器切換至用戶模式,這個特性在M0中沒有。

評論