《Cortex-M0權威指南》之Cortex-M0技術綜述

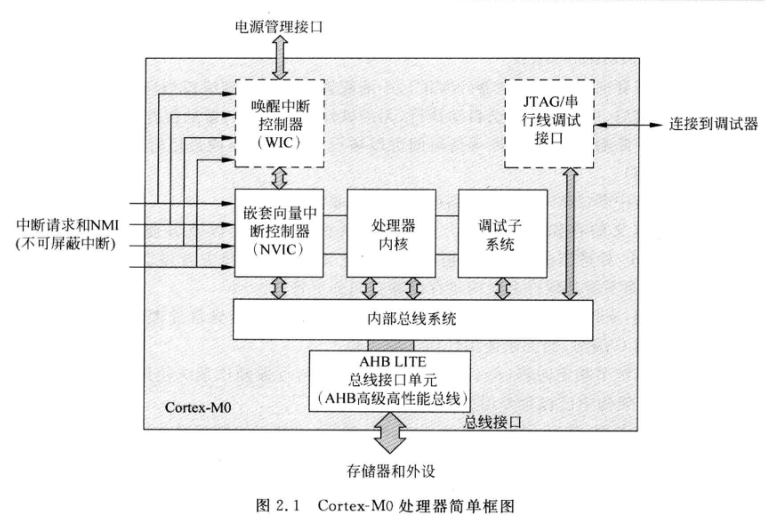

Cortex-M0 處理器簡介

本文引用地址:http://www.104case.com/article/201612/341888.htm1. Cortex-M0 處理器基于馮諾依曼架構(單總線接口),使用32位精簡指令集(RISC),該指令集被稱為Thumb指令集。與之前相比,新的指令集增加了幾條ARMv6架構的指令,并且加入了eThumb-2指令集的部分指令。Thumb-2技術擴展了Thumb的應用,允許所有的操作都可以在同一種CPU狀態下執行。Thumb指令集既包括16位指令,也包括32位指令。C編譯器生成的指令大部分是16位的,當16位的指令無法實現所需要的操作時,32位指令就會發揮作用。這樣以來,在代碼密度得到提升的同時,還避免了兩套指令集之間進行切換帶來的開銷

2. Cortex-M0總共支持56個基本指令,其中某些指令可能會有多種形式。相對于Cortex-M0較小的指令集,其處理器的能力可不一般,因為Thumb是經過高度優化的指令集。從理論來說,由于讀寫存儲是的指令是相互獨立的,而且算數或邏輯操作的指令使用寄存器,Cortex-M0處理器可以被歸到加載-存儲(load-store)結構中。

3. 處理器核心包括:

寄存器組 包含16個32位寄存器,其中有一些特殊寄存器

算術邏輯單元

數據總線

控制邏輯

流水線根據設計可分為三種狀態: 取指、譯碼、執行。

4. 嵌套向量中斷控制器(NVIC)可以處理最多32個中斷請求和一個不可屏蔽中斷(NMI)輸入。

5. NVIC需要比較這個在執行中斷和請求中斷的優先級,,然后自動執行高優先級的中斷。

6. 如果要處理一個中斷,NVIC會和處理器進行通信,通知處理器執行中斷處理程序。

7. 喚醒中斷控制器(WIC)為可選的單元,在低功耗應用中,在關閉了處理器大部分模塊后,微控制器會進入待機裝填,此時,WIC可以在NVIC和處理器處于休眠的情況下,執行中斷屏蔽功能。當WIC檢測到一個中斷時,會通知電源管理部分給系統商店,讓NVIC和處理器內核執行剩余的中斷處理。

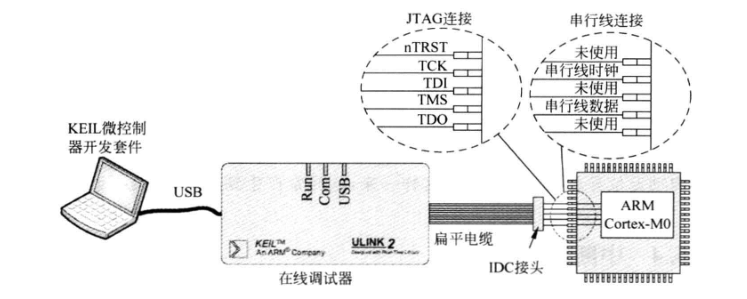

8. 關于調試子系統,當調試事件發生時,處理器內核會被置于暫停狀態,這是開發人員可以檢查當前處理器的狀態。硬件調試工具有JTAG和SWD(串行線調試)。

ARM Cortex-M0 處理器的特性

系統特性

thumb指令集,具有高效和高代碼密度

高性能,最高達到0.9DMIPS/MHz

內置的嵌套向量中斷控制器(NVIC),中斷配置和異常處理容易

確定的中斷響應事件,中斷等待事件可以被設定為固定值或最短事件(最小16個時鐘周期)

不可屏蔽中斷(NMI),對高可靠性系統非常重要

內置的系統節拍定時器(systick)。24位定時器,可被操作系統使用,或者用作通用定時器,架構中已經包含專用的異常類型

請求管理調用,具有SVC異常和PendSV異常(可掛起的管理服務),支持嵌入式os的多種操作

架構定義的休眠模式和進入休眠的指令,休眠特性能大大降低能量的消耗。由于進入休眠狀態需要使用特定的指令,而不是使用寄存器,架構定義的休眠模式也提高了軟件的可移植性。

異常處理可以捕獲到系統中的多種錯誤。

應用特性

中斷數量可配置

支持大端或小端存儲器

可選擇的喚醒中斷控制器(WIC),處理器可以在休眠狀態下掉電以降低功耗,而WIC可以在中斷發生時喚醒系統

評論