一“芯”二用,MCU+DSP處理器大盤點

近年來,越來越多的領域需要用到高性能,高集成度的DSP器件,功能日益增加的多媒體處理器對DSP的需求也日益劇增,于是,基于MCU+DSP架構的集成芯片也隨之應運而生,更低的成本、更小的封裝和更微的功耗所開辟的,是一條屬于DSP或者MCU廠商們的“陽光大道“而未來,它們還將沿著這條新路繼續前行。本系列文章將為你介紹市面上比較流行的基于MCU+DSP架構的處理器或者解決方案。

本文引用地址:http://www.104case.com/article/201612/332400.htm飛思卡爾DSP56800E

飛思卡爾在DSP與MCU領域深耕數年,為滿足市場發展需求,公司率先在56800內核基礎上又推出了新一代增強型內核56800E,該產品可在單一內核上提供DSP和MCU雙重功能。56800E 系列DSP將為不斷增長的工業、電機控制、汽車和融合中的通信與數據通信市場應用提供低功耗、低成本的單芯片方案。由于這種單內核設計消耗更少的功耗,飛思卡爾啟動了大量新的、以電池供電、需要信號處理功能的便攜式應用,如便攜式數字音頻、互聯網設備和PDA等。

DSP56800E相關資料推薦:

1.MC56F8335:基于56800E內核的數字信號控制器

2.基于56800E數字信號處理和霍爾傳感器的三相BLDC電機控制

簡介

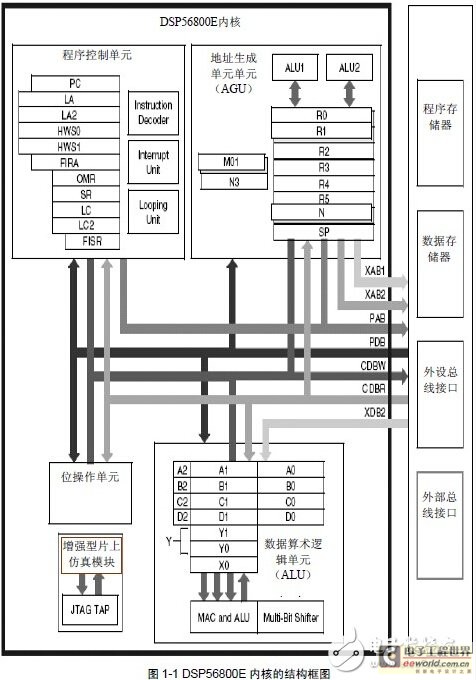

與56800相比,56800E性能最高可改善5倍,為需要更多存儲空間、更高代碼編譯效率和更高的MIPS性能的客戶提供了清晰的產品移植路徑。DSP56800E 由幾個功能獨立的模塊組成。包括:數據算術邏輯單元(ALU),地址生成單元(AGU),程序控制器,位操作單元,強化的片上仿真模塊(Enhanced OnCE)和系統總線。如圖所示。

靈活的內存模式是DSP56800E 結構的一大特色,包括下面的幾個方面:

程序RAM 和ROM 模塊

數據RAM 和ROM 模塊

非易失內存(NVM)模塊

引導ROM,自舉RAM 區執行代碼的模塊

Freescale 的標準片上外圍接口總線(IP-BUS)支持多種的片上外設模塊,包括下面幾個模塊:

鎖相環(PLL)模塊

16 位定時器模塊

看門狗(COP)模塊和實時定時模塊

同步串行接口(SSI)模塊

串行外設接口(SPI)模塊

可編程的通用I/O 口(GPIO)模塊

特性

DSP56800E 結構具有一系列新的特點,用于提高系統性能,降低應用成本,簡化產品開發。包括以下各個方面。

高性能:DSP56800E 支持很多的DSC應用場合。

兼容性:向下兼容DSP56800 系列的源代碼,DSP56800 只需要重新編譯或者重新匯編就可以在DSP56800E 系統上執行。

易編程性:DSP56800E 的指令助記符類似于MCU 的指令助記符,易于從傳統的微控制器編程轉到DSC 編程。為了優化算法的執行,DSP56800E 的指令集支持小數和整數類型。

對高級語言的支持:C 語言編寫的程序非常合適DSP56800E 結構,大部分的應用可以使用高級語言編寫卻不會影響DSC 的性能,靈活的指令集和編程模式使得編譯代碼的高效生成變為可能。

豐富的指令集:除了支持DSC 算法的指令集,DSP56800E 還提供控制、位操作和整型處理等指令,支持多種數據類型和尋址模式。使得用戶方便地生成高效、緊湊的代碼。

高代碼密度:DSP56800E 基本的單字指令長度僅為16 位,而多字指令則用于更復雜的操作,達到優化的代碼密度目的。DSP56800E 指令集強調的是高效控制的編程,因為在一個應用中最大的部分是這方面的操作。

支持多任務:在DSP56800E 上執行一個實時操作系統或者簡單的多任務系統將比其他的DSC 芯片更容易。DSP56800E 完全支持軟件堆棧,快速的從系統堆棧中實現32 位上下文切換,基本的測試和設置指令,四優先級的軟件中斷。

精確性:DSP56800E 具有精確計算的能力。

硬件循環:DSP56800E 提供2 種類型大于0 的硬件循環。提高了性能,使得不再需要使用解開式循環技術。

并行性:每個片上執行單元,內存設備,外圍操作是獨立并行處理的。由于很高的并行性,下面的操作能在1 條指令內被并行執行:

—取下條指令

—16 位乘16 位,并將結果和一個36 位數累加

—可選擇性進行結果取反、四舍五入以及飽和度處理

—2 個16 位數的移動

—無負荷的硬件循環

—2 個地址指針的更新

不可見的指令管道(pipeline):八級指令管道提高了系統的性能,卻保持對編程者的不可見。開發者可以使用高級語言而不需要考慮到管道。

低功耗:由于使用的是CMOS 工藝,DSP56800E 本身消耗的能量是很少的, 而且DSP56800E 支持兩種更加省電模式,STOP 和WAIT 模式。電源管理模塊能關閉那些邏輯上不使用的部分

實時調試:Freescale 的加強型片上仿真技術提供了對DSP56800E 內核的狀態實現了簡單、低價、非入侵、速度無關的存取方式。通過使用這一技術,在不停止內核的運行情況下,編程者能完全的控制處理器的操作,能簡單、高速的完成調試任務。

DSP56800E 的高效指令集和總線結構,擴展的并行性,片上編程和數據內存,先進的調試和測試功能使得內核能很好地解決實時性問題、嵌入式DSC 和控制任務。

內核編程模式

DSP56800E 的內核寄存器被認為是內核編程模式的一部分。如圖2-1 所示。片上模塊的寄存器被映射到數據存儲器的64 個單元上,注意,這64 個單元在特定的設備上可以位于數據存儲器的任何位置。使用內存塊的實例如表2-1 所示。可以參考特定器件的用戶手冊得到其模塊的細節描述,包括它們的功能,存儲區的寄存器及其映射到內存的位置。

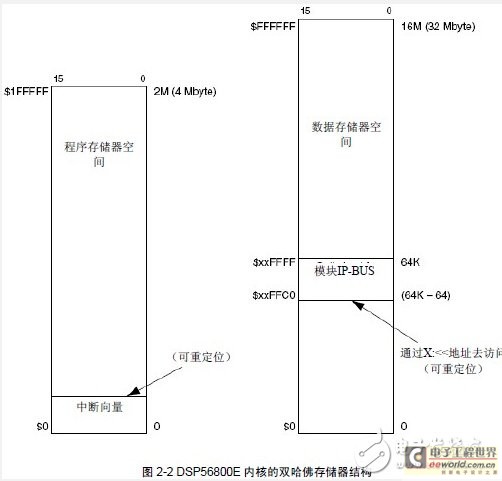

雙哈佛存儲器

DSP56800E 具有程序存儲區與數據存儲區分開的雙哈佛結構,如圖2-2 所示。這種結構允許同時進行對程序存儲區和數據存儲區的讀寫操作,而且數據存儲器支持同時2個地址的讀操作,支持最多達3個地址單元的存儲器操作。

在程序存儲器中,包含了可以任意大小和放在任意位置的復位中斷向量。外設寄存器被映射到數據存儲器的64個字的地址單元。

外設寄存器的64個字的地址單元原則上可以被重映射到任意地址。為了不重疊RAM 和ROM 數據存儲塊,64 個字單元的地址通常被特別設定,X:《《pp 尋址模式提供了針對64 個單元的高效訪問,提供了單字,單周期轉移和位操作指令。

注意在64 個單元的最上面12 個單元被DSP56800E 內核保留使用,用于中斷優先級,總線控制寄存器。

DSC實例

DSC 是一種能對周期性地采樣和數字化的實時信號進行算術的處理器,DSC 實例都包含以下幾個方面:

濾波

卷積(混合兩個信號)

相關(比較兩個信號)

整流,放大和傳輸

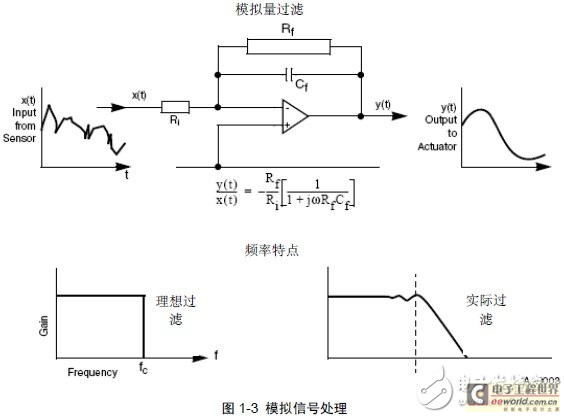

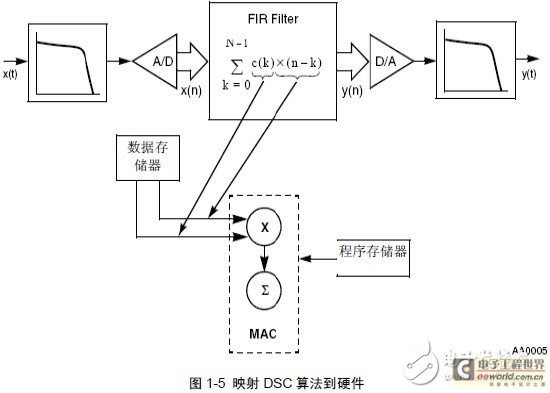

圖1-3 是1 個模擬信號處理的例子。圖中的電路過濾了來自的傳感器的信號,傳感器信號采集電路使用了1 個可調節的放大器,并利用該結果控制1 個動力臂。理想的濾波器是無法設計出來的,工程師設計濾波器時必須盡量滿足:可接受的響應性,不同溫度的變化,元器件老化,電源波動和元器件的精度等因素。按照這樣要求設計出來的電路一般具有很低的抗干擾性,需要經常調整參數且難于修改。

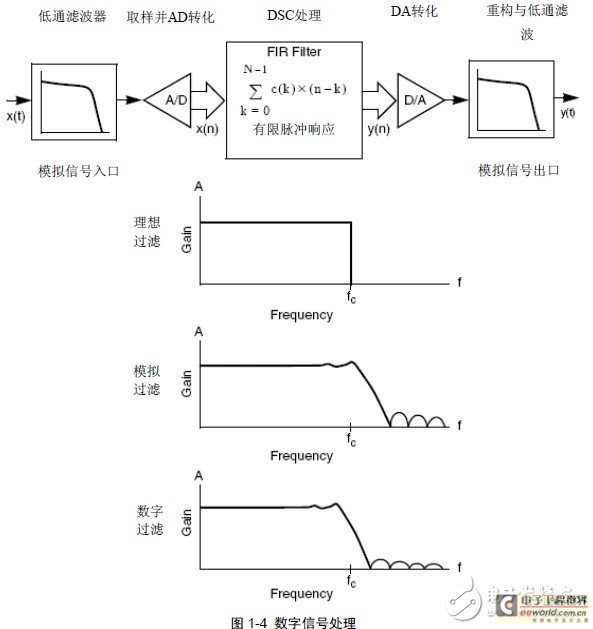

使用 DSC 的等效電路如圖1-4 所示。這個應用除了DSC 之外,還要求1 個A/D 轉化器和D/A 轉化器。

上圖的處理電路首先通過 1 個濾波器限制輸入信號的波段,將去除了超過波段的干擾信號。然后信號被取樣,通過AD 轉換器數字化并送入DSC 進行數字化處理。DSC的輸出通過DA 轉化成模擬信號并通過低通過濾,消除數字化的影響。

通過DSC 執行的特定的濾波嚴格來說是個軟件的過程。DSC 能執行任何使用模擬技術實現的濾波器。而且,使用模擬技術很難實現的自適應性過濾,能很容易的通過DSC 實現。

總之,使用DSC 的優勢如下:

更少的元件

穩定,確定的性能

無需調整濾波系數

廣泛的應用范圍

更加鮮明的過濾特點

抗噪聲能力強

易實現自適應性過濾

具有自測試功能

較好的電源干擾抵制機制

DSP56800E 系列不是為了一個特定的應用專門定制的IC 芯片,而是作為一種通用目的的DSC 結構,用于高效的執行普通DSC 算法和控制代碼。

如圖1-5 所示,DSC 關鍵的屬性如下:

乘法累加(MAC)操作

MAC 的每個指令周期取2 條操作數

強大的指令集保證了執行的靈活性

移入/出DSC 數據

MAC 操作是一個在DSC 中的基本操作,DSC56800E 雙哈佛結構優化了MAC 操作,通過同時對兩個獨立的數據單元存取使得乘法操作和加法操作在一個MAC 時鐘周期內完成。整個過程必須在程序的控制下才能完成從乘法器的取數和對計算結果的轉存。由于內存和MAC 是互相獨立的,DSC 能在一條指令內執行兩個內存的數據交換,一個乘法和加法運算,兩個地址的更新等操作,使得很多DSC 級的處理器能更加高效的執行乘法運算。

評論