基于FPGA和多DSP的多總線并行處理器設計

引言

隨著國防工業對精確制導武器要求的不斷提高,武器系統總體設計方案的日趨復雜,以及電子元器件水平的飛速發展。導引頭信號處理器的功能越來越復雜,硬件規模越來越大,處理速度也越來越高,而且產品的更新速度加快,生命周期縮短。實現功能強、性能指標高、抗干擾能力強、工作穩定可靠、體積小、功耗低、結構緊湊合理符合彈載要求的導引頭信號處理器已經勢在必行。過去單一采用單片機或DSP處理器搭建信號處理器已經不能滿足要求。針對現有技術的不足之處,本文提出一種基于FPGA和3片DSP的目標識別與定位并行處理器。主要解決現在信號處理方法在水中兵器中的應用難題,提高兵器的智能化與戰技指標。

1 系統設計方案

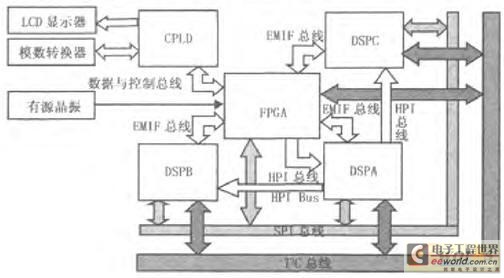

本文設計了一種基于FPGA和3片DSP的目標識別與定位并行處理器。如圖1所示,其特征在于:

(1)端口控制CPLD芯片、系統數據緩存與通信FPGA芯片、3個DSP處理芯片、系統電源模塊、多路并行ADC模數轉換芯片、有源晶體振蕩器、LCD輸出顯示模塊。

(2)將FPGA作為系統數據緩存、通信與控制中樞,以此為核心,通過數據與控制總線聯接端口控制CPLD芯片,通過EMIF總線分別聯接DSP(A)、DSP (B)和DS (C)處理芯片。

(3)端口控制CPLD芯片的輸入端聯接多路并行ADC模數轉換芯片,輸出端口聯接LCD輸出顯示模塊。

(4)有源晶體振蕩器與FPGA芯片聯接,FPGA芯片將有源晶體振蕩器分為4路時鐘信號輸出,分別輸出到CPLD和3片DSP芯片。

(5)系統電源模塊為5V單電源供電,產生系統需要的3. 3V、2.5V、1.2V電源電壓。

(6)多路并行ADC模數轉換芯片對陣列接收信號進行采集,將采集的數據傳輸到CPLD緩存空間中,CPLD緩存空間半滿后將數據傳輸到FPGA數據存儲FIFO中,并將數據轉換為復數數據保存;

(7) DSP (A)、DSP (B)和DSP (C)處理芯片對于采集的數據采用并行分離算法進行盲分離和盲解卷積定位,然后對盲分離各信號進行支持向量機分類,DSP (A)、DSP (B)和DSP (C)處理芯片分別并行對待識別分離信號進行3類艦船的信號的識別,比較3個DSP的識別結果,完成目標信號分類,將分離信號識別完畢,輸出至FPGA綜合定位與分類結畢,并將結果通過CPLD輸出到LCD顯示。

圖1系統原理圖

多通道ADC對陣列接收信號進行采集,將采集數據傳輸到CPLD緩存空間中,CPLD緩存空間半滿后將散據傳輸到FPGA數據存儲FIFO中,井將數據轉換為復數數據保存,等待處理,從而實現了ADC的連續高速采集,一批數據采集完成后,用3DSP盲信號并行分離算法進行盲分離和盲解卷積定位,之后.對盲分離各信號進行支持向量機分類,3片DSP分別并行對待識別分離信號進行3類艦船的信號的識別,比較3個DSP的識別結果,完成目標信號分類,直到講待分類的分離信號識別完畢,最后由FPGA綜合定位與分類結果,并將結果通過CPLD輸出到LCD顯示。

2 具體系統設計

FPGA在實時并行計算實現標準數字信號處理算法的能力遠強于DSP,因此數字接收系統信號處理要用到的FIR濾渡、FFT、IFFT等算法,在FPGA中實現要遠快于DSP,且FPGA廠商提供了非常豐富易用的能實現數字信號處理的參數Core,可以大大簡化開發過程。而且,FPGA有大量乘法器和存儲器資源,支持設計高度并行的架構,可有效提高實時性、集成度和穩定性。而DSP用來進行其他復雜信號處理,比如自動目標識別、抗干擾等。

2.1電路構成

本系統包括一片端口控制CPLD芯片,一片系統數據緩存與通信FPGA芯片,三片DSP處理芯片,一片串口通信芯片,一片USB通信芯片,一片3.3V電源芯片,一片2.5V電源芯片,一片1. 2V電源芯片,一片多路并行ADC模數轉換芯片.一片多路并行DAC數模轉換芯片,一片Flash存儲器,三片SRAM存儲器,一片EPCS存儲器,一個有源晶體振蕩器.一個無源晶體振蕩器,一個PS2鍵盤接口,一個USB接口,一個申口接口,一個SD卡卡座,一個LCD顯示模塊.

DSP芯片:TMS320C6713 DSP是TI推出的一款C6000系列32位高速浮點型DSP芯片,時鐘最高頻率為225MHz,最大處理能力達到2400MIPS,采用二級緩沖處理,4kByte直接匹配的程序緩沖LIP.4kByte可匹配的數據緩沖LID,256kByteL2額外匹配內存。32位外部存儲器接口,可無縫連接SRAM,EPROM、Flash、SBSRAM和SDRAM;其外設EDMA支持無需CPU參與可以在允許的地址空間里傳送數據,擴展總線,具有主機口和I/O端口操作等功能,多通道緩沖串口,其通過配置能和多種串行通信接口通信。兩個32位通用定時器等。

FPGA芯片:EP3C25Q240C8N是ALTERA推出的一款功耗最低、成奉最低的Cyclone III系列高性能FPGA,具有24,624個邏輯單元,66個M9K存儲塊,總共608,256 Bits的RAM,66十18 *18乘法器,4個PLL,另外,其內部還有20個可獨立工作的時鐘網絡,240個外部引腳提供了148個通用I/O,可以完全滿足多DSP的互聯。其豐富的內部資源可以提供多種數據交換模式,進一步采用嵌入式Nios II處理器,其本身亦可以作為強大的數據處理器使用,配個其并行的計算結構和較高的運行頻宰,特別適合效據先期處理的計算處理器使用。

CPLD芯片:EPM3128ATI100 -10N是ALTERA推出的一款基于CMOS EEPROM結構的MAX 3000A系列的高性能可編程器件,具有2,500可用邏輯門,128個宏單元,多大98個可用I/O口,最高時鐘頻率192. 3MHz,接口電壓兼容Sv.3.3V,2.SV等,是理想的數據轉換與通信控制器件,系統中用于擴充FPGA的I/O口,作為數據轉換、緩沖與通信橋路。

評論