一種智能ARI NC429總線接口板的硬件設計與實現

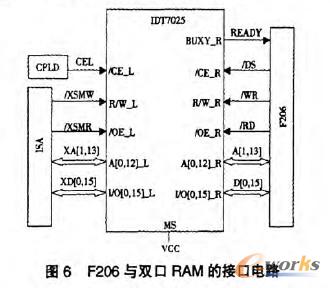

5 F206與雙口RAM的接口電路

當接口板實現數據的發送功能時,數據首先從ISA總線讀入,并存儲在雙口RAMIDTT025中,當適合發送數據時,F206發出讀取信號,將存儲在IDT7025中的數據通過DO~D15數據總線傳輸給HS3282,通過HS3282控制向429總線發送數據;同樣,在接收數據時,HS3282接收的數據在砣06的控制下,通過數據總線DO,D15傳輸到IDT7025中,最后Pc機通過ISA總線接收數據,從而完成數據的收發功能。圖6中,READY為高,表明對雙口RAM的訪問可以結束,否則將延續此次訪問。

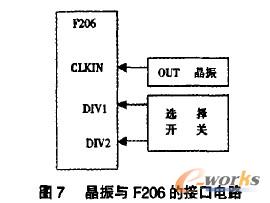

6 F206的時鐘電路

DSP時鐘可由外部提供,也可由板上的振蕩器提供。但一般DSP系統中,經常使用外部時鐘輸入,因為使用外部時鐘時,時鐘的精度高、穩定性好、使用方便,從而可以保證DSP能夠可靠、穩定的工作。而且,使用外時鐘時,可以通過改變DIVI、DIV2引腳上的電平,設置時鐘方式為×1、×2或×4。這樣,只需用一個時鐘。就可以提供DSP的多個工作時鐘,增加了系統的靈活性。這里我們選用20M的晶振,并用選擇開關來成比例的設置DSP的工作時鐘。接口電路如圖7所示。

7 仿真接口電路

DSP和CPLD都是通過仿真接口JTAG進行在線編程的。JTAG(Joint Test Action Group)是檢測PCB和IC芯片的一個標準,通過這個標準,可對具有JTAG接口芯片的硬件電路進行邊界掃描和故障檢測。YrAG接口的設計比較簡單,只要根據芯片所提供的接口類型按照相應的接口標準即可。

8 結束語

通過整個設計方案可以看出.用DSP+CPLD模式實現429總線和ISA總線之間的數據通訊,省去了EPROM、RAM、地址數據鎖存器等外圍電路,使得原理圖的設計簡單、清晰。合理地使用CPLD。又增強了板卡的集成度和開發的便利性。通過開發和調試證明,該板卡能夠滿足高速ARINC 429數據傳輸的要求,并且執行速度快,體積小,集成度高。可靠性好。

評論