基于PCI總線的HDLC通信卡的設計與實現

PCI總線及在其基礎上發展起來的CPCI總線,在工業控制、數據采集、信息通信、航空航天等領域得到了廣泛的應用。高級數據鏈路控制(HDLC)是一個在同步網上傳輸數據并面向位的數據鏈路層協議,具有透明傳輸、可靠性高、傳輸效率高以及靈活性高等特點,可以實現點到點或者點到多點的數據傳輸,在路由器、網關等通信或者網絡設備中應用廣泛。為了滿足實際工作的需要,并為后續系統升級提供拓展空間,本文設計并實現了一款基于PCI總線、符合HDLC協議的通信卡,以滿足高速數據傳輸的需要。通信卡采用PCI總線控制器實現PCI總線接口設計,采用FPGA實現HDLC通信協議及接口邏輯設計,采用RS一422標準對外通信,實現與外系統的互連。

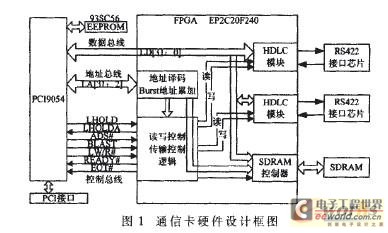

1 HDLC通信卡總體方案

通信卡主要采用PCI9054和FPGA構成硬件系統,其硬件結構圖如圖1所示。數據傳輸流程為:接收數據時,通過RS一422接口芯片接收數據,數據格式滿足簡化的HDLC協議;通過FPGA內部的HDI.C模塊進行數據接收和串并轉換;然后在本地控制邏輯的控制下通過PCI9054以DMA方式傳給上位機,實現數據的接收和判讀;發送數據時,上位機軟件將數據以DMA方式傳給PCI9054再輸入FPGA,在其內部HDLC模塊的作用下,進行數據并串轉換和HDLC協議轉換,最后通過RS一422發送器進行電平轉換和數據發送。預留SDRAM以滿足大容量數據通信需要。

2 HDLC通信卡電路設計

2.1 總線接口設計

PCI總線具有高性能、低成本、開放性、兼容性良好等優點,但PCI總線具有嚴格的時序關系和電氣規范,使得開發工作量和難度比較大。PCI總線一般都采用各IC生產商設計的PCI專用接口芯片進行PCI總線設的開發,以減少開發難度、降低上作量。基于此考慮,在本設計中,采用PLX公司的PCI9054芯片進行總線開發。

PCI9054芯片滿足PCI V2.2協議,可作為橋接芯片在PCI總線和本地總線(10cal bus)之間提供信息傳輸,既可以作為兩個總線的主控設備去控制總線,也可以作為兩個總線的目標設備去響應總線。其本地總線可工作在M、C、J三種模式,可方便地與多種微處理器連接。在C模式下,因本地總線的地址線和數據線分開,時序與控制邏輯比較簡單,得到了廣泛應用[31。因此本通信卡中,PCI9054工作于C模式從設備方式,本地總線時鐘采用40 MHz恒溫補償晶振。PCt9054的PCI總線端引腳按照對應關系與PCI總線金手指連接器相連,本地端地址總線為15 bit,數據總線為32 bit,控制總線包括ADS、BLAST、LHOLD、LHOLDA、LW/R#、READY、EOT#引腳,將它們分別與FPGA的10口互連。

2.2 FPGA芯片選型與設計

HDLC協議是面向比特的高級數據鏈路控制規程,具有強大的差錯檢測功能、高效和同步傳輸的特點,利用它可以確保數據信息可靠互通。市場上有許多使用簡單的專用HDLC芯片,但由于HDLC標準的文本較多,這些芯片出于專用目的難以通用于不同版本,缺乏應用靈活性,且其片內存儲器容量有限。另一種方法是通過軟件對MCU編程實現HDLC協議,雖然功能靈活、適應性強,但處理速度慢、占用處理器資源多,難以高速實現對HDLC數據的插“0”和去“0”操作,一般只適用于路數較少的低速場合141。

為了實現與當前系統HDLC協議的兼容,本通信卡采用FPGA實現HDLC收發功能模塊,充分利用FPGA硬件可編程的特點,發揮其速度快、靈活性高、并行處理信號、實時性能夠預測的優勢。同時,考慮到通信卡傳輸一幀數據的長度通常為512 KB~1 KB,而PCI9054的DMA只有32長字FIFO,且PCI讀寫速度與HDLC收發速度不一致,需要利用FIFO進行數據緩存,達到時序匹配的目的。為了提高系統集成度及其可靠性,采用FPGA內部存儲單元實現FIFO功能。因此,綜合考慮FPGA內部存儲單元數量、10引腳數量等,選擇Altera公司的EP2C20一F240用于功能模塊開發。EP2C20F240為QFP封裝,可用IO口142個,內部LE 18 752個,內部RAM為239 616 bit,可以滿足系統開發需要。

2.3 差分接口設計

通信卡對外通信采用RS一422方式傳輸數據,傳輸頻率最高為768 kHz。因此,選用MAXIM公司的RS一422發送器MAX3032E和接收器MAx3094E,其數據傳輸率最高分別可達20 Mb/s和10 Mb/s,滿足數據高速傳輸需要。

3 HDLC通信卡邏輯設計

通信卡上的FPGA完成PCI9054本地總線數據讀寫時序邏輯的轉換,實現HDLC收發模塊和FIFO數據緩存功能。設計中采用VHDL硬件描述語言實現各功能模塊,利用Ahera公司的集成開發環境Quartus II(11.0)完成相關的編譯、調試、下載等開發工作。

3.1 本地總線數據讀寫模塊

PCI9054工作于C模式從設備方式,采用分散/聚合(Scatter—Gather)DMA方式進行數據快速傳輸,以發揮其速度快的優勢。根據PCI9054讀寫時序圖可知,在C模式從設備方式下,FPGA讀取PCI9054本地端ads_n和hlast_n的引腳狀態,判斷是單周期讀寫狀態還是猝發讀寫狀態,實現地址獲取和數據讀寫,其狀態機如圖2所示。同時,在上位機讀數據完畢后,如果讀FI.FO為空則將EOT#引腳拉低,將數據傳輸結束信號上傳,強行停止主機數據讀操作。這就需要在DMA初始化過程中,設置DMAMODE寄存器的第14位為EOT#有效模式。

評論