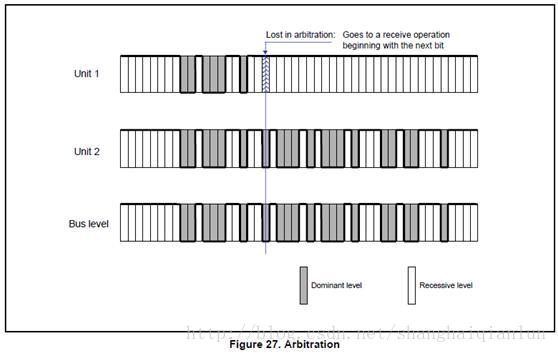

1.7 優先級的決定

在總線空閑狀態,最先開始發送消息的單元獲得發送權。

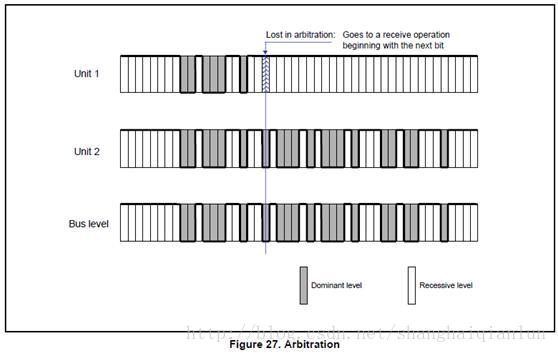

多個單元同時開始發送時,各發送單元從仲裁域的第一位開始進行仲裁。連續輸出顯性電平最多的單元可繼續發送。丟失競爭的單元在下一bit進入接收操作。

仲裁的過程如圖27所示。

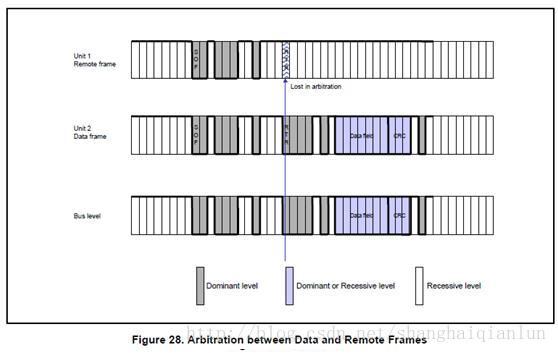

(1)數據幀和遙控幀的優先級

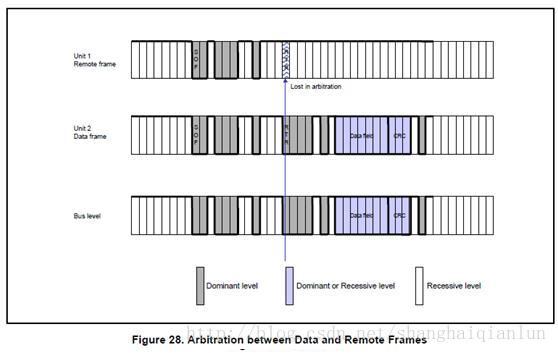

具有相同 ID 的數據幀和遙控幀在總線上競爭時,仲裁段的最后一位(RTR)為顯性位的數據幀具有優先權,可繼續發送。

數據幀和遙控幀的仲裁過程如圖28所示。

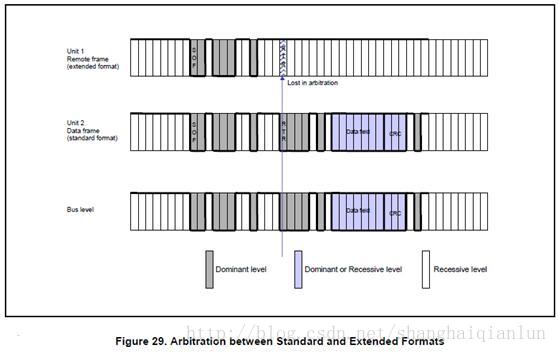

(2)標準格式和擴展格式的優先級

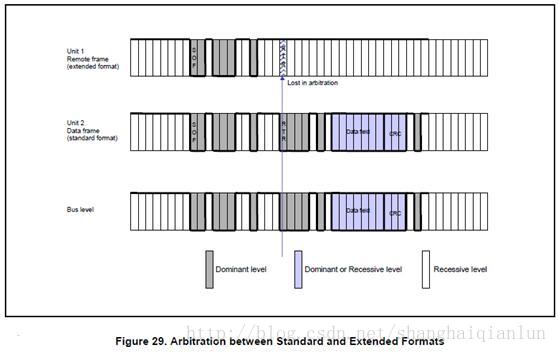

標準格式 ID 與具有相同ID 的遙控幀或者擴展格式的數據幀在總線上競爭時,標準格式的RTR 位為顯性位的具有優先權,可繼續發送。

標準格式和擴展格式的仲裁過程如圖29所示。

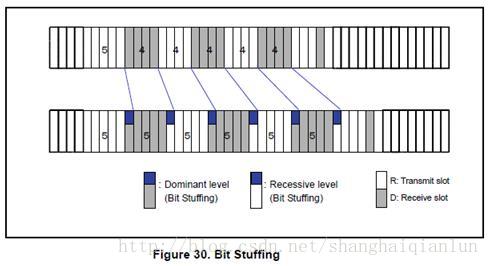

1.8 位填充

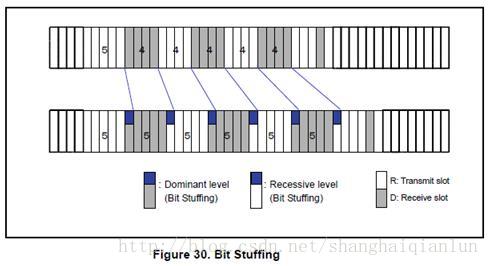

位填充是一種周期性重同步收/發操作的功能,為了防止接收節點間時序由于累積而導致的錯誤,如果5個bit持續了同樣的電平,則添加1個bit的反向數據位。

如圖30顯示的位填充機制:

(1)發送單元的操作

在發送數據幀和遙控幀的時候,SOF-CRC段間的數據,相同電平如果持續5bit,在下一bit(第6bit)則要插入1bit與前5bit反向的電平。

(2)接收單元的操作

在接收數據幀和遙控幀的時候,SOF-CRC段間的數據,相同電平如果持續5bit,需要刪除下一bit(第6bit)再接收。如果這第6bit的電平與前5bit相同,則被視為錯誤,且發送錯誤幀。

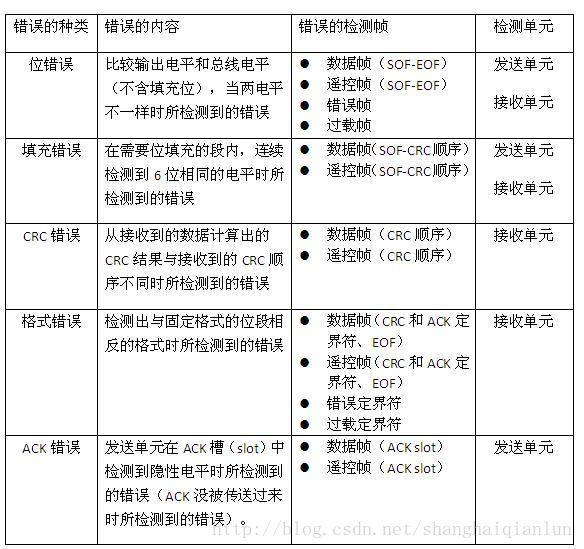

1.9 錯誤的種類

有5種類型的錯誤,可能有2個或更多的錯誤同時發生:

表8列出了這些錯誤的種類、內容、錯誤檢測幀和檢測單元。

- 位錯誤由向總線上輸出數據幀、遙控幀、錯誤幀、過載幀的單元和輸出ACK的單元、輸出錯誤的單元來檢測。

- 在仲裁段輸出隱性電平,但檢測出顯性電平時,將被視為仲裁失利,而不是位錯誤。

- 在仲裁段作為填充位輸出隱性電平時,但檢測出顯性電平時,將不視為位錯誤,而是填充錯誤。

- 發送單元在ACK 段輸出隱性電平,但檢測到顯性電平時,將被判斷為其它單元的ACK 應答,而非位錯誤。

- 輸出被動錯誤標志(6 個位隱性位)但檢測出顯性電平時,將遵從錯誤標志的結束條件,等待檢測出連續相同6 個位的值(顯性或隱性),并不視為位錯誤。

(2) 格式錯誤

- 即使接收單元檢測出EOF(7 個位的隱性位)的最后一位(第8 個位)為顯性電平,也不視為格式錯誤。

- 即使接收單元檢測出數據長度碼(DLC)中9∼15 的值時,也不視為格式錯誤。

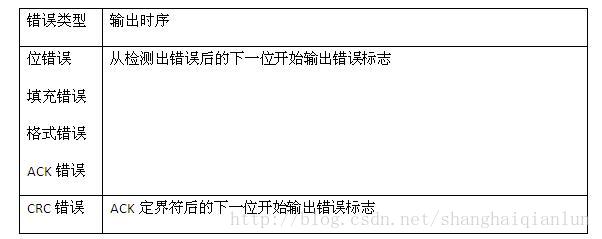

1.10 錯誤幀的輸出時序

檢測到發生錯誤的單元輸出一個錯誤標志,以通知其它單元。

處于主動錯誤狀態的單元輸出的錯誤標志為主動錯誤標志;處于被動錯誤狀態的單元輸出的錯誤標志為被動錯誤標志。

發送單元發送完錯誤幀之后,將再次發送數據幀或遙控幀。

錯誤標志輸出時序如表9:

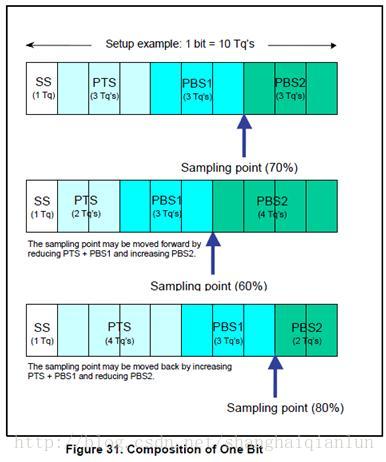

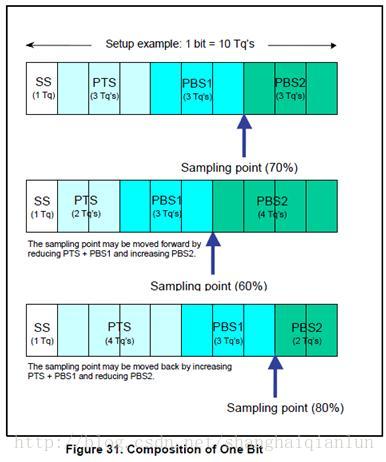

1.11 位時序

在沒有重新同步情況下,發送單元每秒傳輸的位數稱之為位速率。1位由下面4個段組成。

- 同步段(SS)

- 傳播時間段(PTS)

- 相位緩沖段1(PBS1)

- 相位緩沖段2(PBS2)

這些段又由稱之為Time Quantum(以下稱為Tq)的最小時間單位構成。

1位分為4個段,每個段由若干個Tq構成,這稱為位時序。

1位由多少個Tq構成、每個段由多少個Tq構成等是可以設定的。通過設置bit時序。使得可以設定一個采樣點以使總線上多個單元可同時采樣,所謂采樣點就是在這一時刻總線上的電平被鎖存,這個鎖存的電平作為位的值。采樣點的位置在PBS1的結束處。

表10描述了各段的作用和Tq 數。1個位的構成如圖31所示。

段名稱 | 段的作用 | Tq數 |

同步段(SS) | 多個連接在總線上的單元通過此段實現時序的定時調整,以便同步進行接收和發送的工作。 隱性電平到顯性電平或顯性電平到隱性電平變化的邊沿被期望出現在本段。 | 1 | 8-25 |

傳播時間段(PTS) | 用于吸收網絡上的物理延遲的段。包括發送單元的輸出延遲、總線上信號的傳播延遲、接收單元的輸入延遲。 這個段的時間是以上延遲時間累加和的兩倍。 | 1-8 |

相位緩沖段1(PBS1) | 當信號邊沿不能出現在SS 段時,此段用來矯正誤差。 由于各單元以各自獨立的時鐘來工作,細微的時鐘誤差都會累積起來,PBS 段可用于吸收此誤差。 為了吸收一個時鐘誤差,在SJW設置的范圍內增減PBS1和PBS2,PBS1和PBS2越大,允許誤差越大,但是通訊速度會降低。 | 1-8 |

相位緩沖段2(PBS2) | PBS1或IPT中較大者(見注1和2) |

重新同步跳轉寬度(SJW) | 因時鐘頻率偏差、傳送延遲等原因,某些單元可能會失去同步。SJW是所能校正的最大失去同步的寬度。 | 1-4*PBS1 |

注1:IPT代表信息處理時間,是以采樣點作為起始的時間段,用于計算后續位的位電平。這是硬件在一個采樣點后立刻改變位的電平所必須要的。這個時間等于或小于2Tq,。

注2:因為采樣點是處于PBS1結束處,所以IPT和PBS2重疊。當IPT = 2Tq時,PBS2不可能選為1,因此,PBS2必須是2到8Tq。

注3:重新同步的結果使相位緩沖段1增長,或使相位緩沖段2 縮短。相位緩沖段加長或縮短的數量有一個上限,此上限由SJW(重新同步跳轉寬度)給定。重新同步跳轉寬度應設置于1和最小值之間(此最小值為4*PBS1)。

可以從一位值轉換到另一位值的過渡過程得到時鐘信息。這里有一個屬性,即:只有后續位的一固定最大數值才具有相同的數值。這個屬性使總線單元在幀期間重新同步于位流成為可能。可用于重新同步的兩個過渡過程之間的最大的長度為29個位時間。

1.12 同步是如何獲得的?

CAN總線的通訊是采用NRZ(Non-Return to Zero,非歸0)碼,數據本身并不攜帶時鐘信息,也即在每一位的開始或結束沒有同步信號,發送單元以位時序同步的方式開始發送幀數據,接收單元根據總線電平的變化進行同步并進行接收工作。

然而,發送器和接收器之間由于彼此的時鐘誤差或傳輸路徑的相位誤差可能會失去同步關系,因此接收單元在接收幀的時候,必須通過硬件同步或重新同步調整它的操作時序。

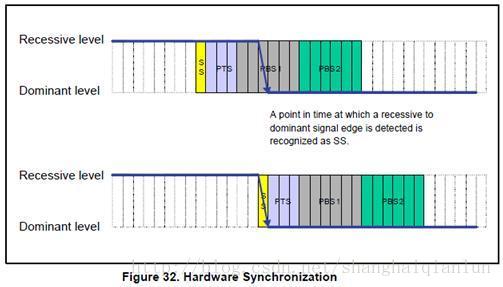

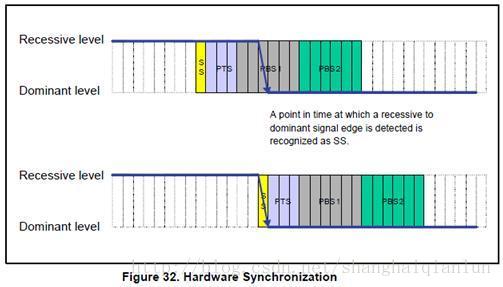

1.13 硬件同步

在總線空閑狀態時,接收單元檢測到SOF,就會執行這個同步調整過程。“隱式”電平跳變到“顯式”電平的邊緣的時間點被認為是SS,而不管SJW的值

圖32顯示了硬件同步機制。

- 如果沿出現在SS里,沿的相位誤差e=0;

- 如果沿位于采集點(PBS1結束之前)之前,e>0;

- 如果沿位于采集點之后,e<0;

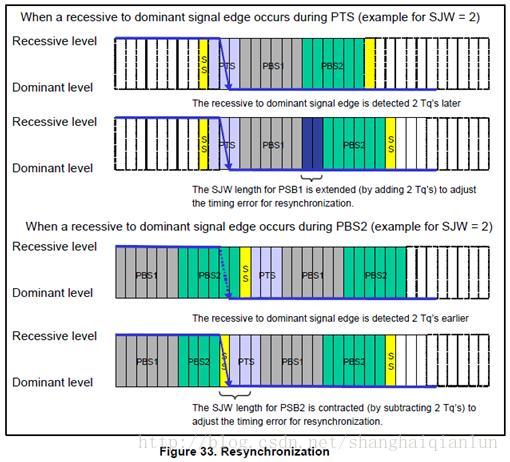

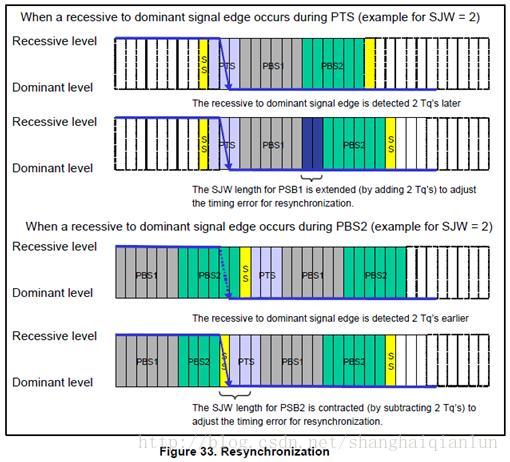

1.14 重新同步機制

在接收過程中檢測到總線電平發生了改變時執行重新同步操作。

每當檢測到一個邊沿(總線電平的改變),收發單元根據SJW值通過增加PBS1段或減少PBS2段,來調整同步。但,如果發生了超出SJW值的誤差時,最大調整量不能超過SJW值。

圖33顯示了重新同步機制。

1.15 調整同步的規則

硬件同步和再同步的執行遵從如下規則:

1) 在1個位時間里(或者說在2個采樣點之間),只允許一個同步(或者說只進行一次同步調整)。

2) 只有當采樣點之前的總線電平和邊沿后的總線電平不同時,該邊沿才能用于調整同步。

3) 如果出現隱性電平到顯性電平變化的邊沿,且條件(1)和(2)滿足,將進行同步。

4) 如果在幀間間隙期間發生隱性電平到顯性電平的信號邊沿(除了間隙里的第一位),則總會執行硬件同步。

5) 如果發生從所有其它隱性電平到顯性電平的信號邊沿,則執行再同步。

6) 如果發送單元自身輸出的顯性電平被檢測到有延遲,則不執行再同步。

評論