高速串行總線知多少…

表1:重要的串行總線標準

表1:重要的串行總線標準每個規(guī)范定義了產(chǎn)品必須符合標準的要求,包括電氣、光學、機械、互連等等。管理機構發(fā)起標準化測試,來檢驗產(chǎn)品是否能通過標準要求。這些測試可能會詳細到了指定具體的測試設備。標準不斷發(fā)展,因此參數(shù)規(guī)格不斷的修改。必須保持目前對產(chǎn)品的測試和規(guī)范的要求一致。

我參與許多標準組織并在不同的工作組中和其他公司一道,幫助管理機構制定有效的測試過程和符合性測試流程。

在這份文檔中,我們會提到以下三個標準。泰克公司作為工作組的一員,參與到這些標準的制定中。

SATA

SATA接口是一個標準的串行存儲接口,廣泛應用于在今天的臺式機和其他計算平臺。最初的速率只用 1.

5Gbps,但最近更新到 3.0Gbps 的第二代規(guī)范,已經(jīng)進入市場。下一代標準規(guī)定速率是 6Gbps,部分規(guī)范正在業(yè)內制定中。

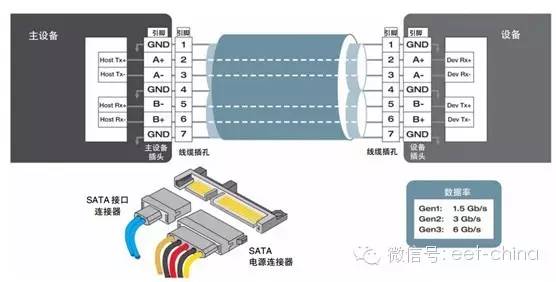

圖1.SATA總線的機械結構

圖1.SATA總線的機械結構像 許多串行標準,S A T A 接口采用低電壓差分信號(LVDS)和8b/10b編碼。數(shù)據(jù)在發(fā)射端和接收端之間采用全雙工的數(shù)據(jù)通道,分別由一條發(fā)送通道(Tx)和一條接收通道 (Rx)組成。SATA 接口采用了擴頻時鐘(SSC)嵌入式時鐘方法,不提供單獨的參考時鐘傳送給接收端。

PCI Express

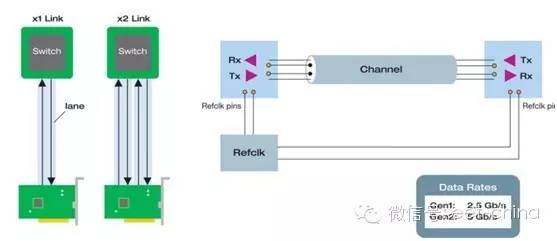

PCI Express已經(jīng)取代PCI成為大多數(shù)芯片到芯片級的應用或電路板傳輸和電纜連接中系統(tǒng)中使用。PCIe 是一個高度可擴展的架構,提供從1到16條全雙工的PCIe連接。在多通道應用,數(shù)據(jù)流根據(jù)現(xiàn)有可用通道的情況而拆分,同時在多個通道上傳輸。最快的 PCIe 應用通常是圖像處理應用,通過 16條高速通道,在系統(tǒng)芯片組和圖形處理器之間傳輸高分辨率的圖形數(shù)據(jù)。圖2描述了 PCI Express 架構。

圖2.PCI Express架構

圖2.PCI Express架構第一代的每條通道傳輸速率是 2.5Gbps,第二代 PCIe2.0提供5Gbps的速率。很快第三代PCI Express提供8Gbps 的傳輸速率。PCIe 不僅采用嵌入的時鐘,還將參考時鐘傳輸?shù)浇邮斩俗鳛?PLL 參考時鐘。

HDMI

高清多媒體接口(HDMI)是第一個專為滿足消費娛樂系統(tǒng)市場而推出的串行總線標準。HDMI接口建立在非常成功的數(shù)字視頻接口(DVI)之上,并延伸了更多功能,集成了更多的娛樂設備,如大屏幕、高清電視和家庭影院系統(tǒng)。圖 3 描述了 HDMI 接口架構。

圖3.HDMI架構

圖3.HDMI架構HDMI 是一個單向傳輸?shù)募軜嫞瑥脑炊讼蚪邮斩藗魉透叻直媛室曨l和多聲道音頻。該規(guī)范定義了三個高速串行數(shù)據(jù)通道,根據(jù)顯示分辨率,傳輸速率從250 Mbps到3.4 Gbps 不等。為了追求更高的數(shù)據(jù)速率和更高的分辨率,在機械部分規(guī)格定義了 Type B 型連接器,將兩個 HDMI 接口并聯(lián),產(chǎn)生了最大吞吐量為 6.8Gbps 的數(shù)據(jù)流。

雖然大多數(shù)高速串行標準依靠 LVDS 信號格式和 8b/10b編碼,但HDMI接口使用的是過渡時間最小化差分信號(TMDS),以減少鏈接上信號的跳變,從而減少電磁干擾(EMI) 。

HDM 接口采用了參考時鐘的設計,時鐘頻率為數(shù)據(jù)率的十分之一。低速串行總線 (I2C總線),稱為DDC的總線,在源端和接收端進行配置和識別時進行雙向信號傳輸。

串行總線結構的基本要素

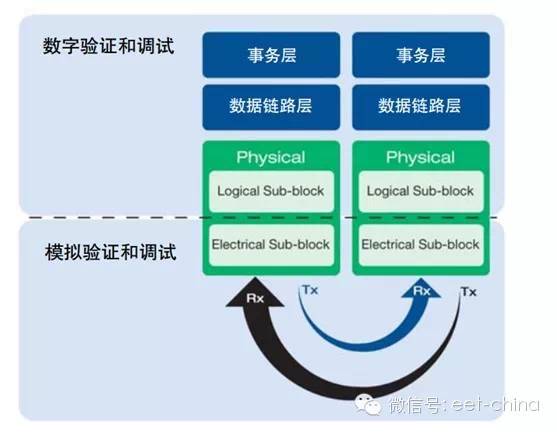

所有的串行總線結構遵循一個多層模型,正如圖 4 所示。物理層有電氣子層和邏輯子層構成。本文主要討論的是電氣子層上所進行的一致性測試。

圖4.速串行總線分層模型

圖4.速串行總線分層模型很多高速串行標準的電氣子層有如下要點:

◆差分信號傳輸,提供良好抗干擾能力

◆8b/10b 編碼減小 EMI,改善信號完整性

◆嵌入式時鐘和參考時鐘一起使用

◆通過擴頻時鐘進一步減小時鐘的 EMI 問題

◆典型的測量包含抖動、幅度、差分對間延時、上升 /下降時間和共模電壓

◆規(guī)范和測試需求隨著標準不斷發(fā)展而演進

表 2:串行總線構架要素總結

表 2:串行總線構架要素總結

評論