基于Virtex-6 FPGA的三種串行通信協議測試及對比 (二)

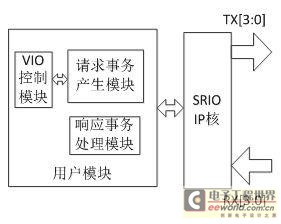

FPGA模塊結構如圖10所示。通過VIO控制模塊,可對包事務類型、包載荷、發送地址等參數進行設置。本測試將包載荷設為256字節,讀/寫內存空間設為DSP的MSM(Multi-core Shared Memory)空間。

本文引用地址:http://www.104case.com/article/201612/326824.htm

圖10 SRIO 2.0通信測試FPGA模塊結構

DSP方面,需要進行相關寄存器的配置,完成SRIO的初始化,使DSP作為目標端處理FPGA發來的SRIO讀/寫請求。DSP主要配置流程包括使能SRIO接口,串并轉換模塊,鏈路數目,鏈路線速率,設備ID等參數的設置。

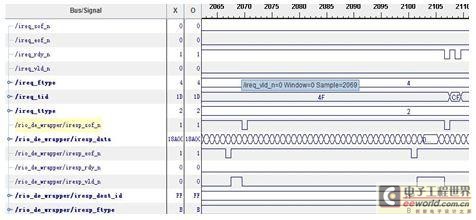

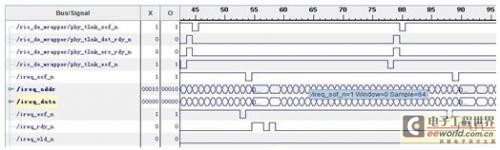

使用ChipScope軟件觀察FPGA相關信號,如圖11,圖12所示。

圖11 SRIO 2.0讀測試信號波形

圖12 SRIO 2.0寫測試信號波形

本測試中,FPGA每連續發送16384個SWRITE或NREAD包后,都會向DSP再發送1個門鈴消息。因此,可以通過計算DSP收到的相鄰兩個門鈴的時間間隔來計算SRIO讀/寫速率。

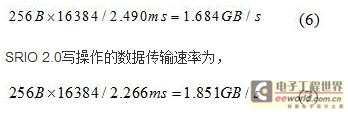

經測算,當FPGA執行SRIO讀/寫操作時,DSP接收的相鄰兩個門鈴的平均時間間隔為分別為2.490ms,2.266ms.故SRIO 2.0讀操作的數據傳輸速率為,

下面計算本測試條件下SRIO讀/寫的理論數據傳輸速率和實際通信效率。

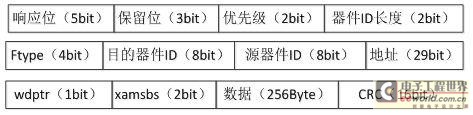

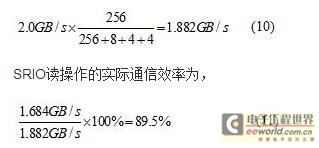

SRIO 2.0協議的主要開銷為物理層編碼開銷和數據包開銷。本測試采用8位路由和34位偏移地址。該條件下SWRITE事務、RESPONSE事務的數據包結構分別如圖13、圖14所示。

圖13 SRIO 2.0 SWRITE包結構

圖14 SRIO 2.0 RESPONSE包結構

由圖13可知,FPGA每發送一個SWRITE包,會帶來10字節的開銷,另外,DSP會返回一個4字節確認接收符號。故本測試中SRIO寫操作的理論數據傳輸速率為,

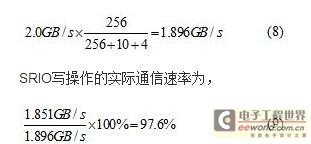

與PCIe 2.0類似,SRIO 2.0可以流水地處理多個未完成的操作,應答開銷與發送開銷之間沒有競爭。故而SRIO 2.0讀操作可只考慮RESPONSE包開銷而忽略NREAD包開銷。由圖14可知,DSP每返回一個RESPONSE包,會帶來8字節的開銷。另外,DSP接收到NREAD包后,會返回一個4字節確認接收符號,FPGA接收到響應包后,也會返回一個4字節確認接收符號。故本測試中SRIO讀操作的理論數據傳輸速率為,

SRIO讀操作的實際通信效率較低的原因是DSP響應FPGA讀請求的時間較長。

SRIO讀操作的實際通信效率較低的原因是DSP響應FPGA讀請求的時間較長。6三種協議的分析比較

本測試中,Aurora 8B/10B、PCIe 2.0、SRIO 2.0均實現了在4x模式下的高速數據傳輸。下面將結合測試結果和協議的具體內容,從以下各方面對三種協議進行比較。

(1)協議分層結構

Aurora 8B/10B協議僅定義了鏈路層和物理層。屬于較為底層的協議。SRIO 2.0協議定義了物理層,傳輸層和邏輯層,PCIe 2.0協議定義了物理層,數據鏈路層,事務層和軟件層,這兩種協議的內容和功能均比Aurora 8B/10B協議復雜。

(2)鏈路數目和鏈路線速率

Aurora 8B/10B協議在鏈路數目和鏈路線速率選擇上比較靈活,鏈路數目可以在1x至16x之間自由選擇,鏈路線速率可以在0.5Gb/s到6.6Gb/s間自由選擇。PCIe 2.0支持1x,2x,4x,8x,12x,16x,32x鏈路,鏈路線速率支持2.5Gb/s和5.0Gb/s.SRIO 2.0支持1x、2x、4x、8x和16x鏈路,鏈路線速率支持1.25Gb/s、2.5Gb/s、3.125Gb/s、5.0Gb/s和6.25Gb/s.

綜上可知,在鏈路線速率選擇范圍的廣泛性和靈活性上,

Aurora 8B/10B>Srio 2.0>Pcie 2.0,

鏈路數目選擇的靈活性上,

Aurora 8B/10B>Pcie 2.0>Srio 2.0.

最大允許的鏈路數目上,

Pcie 2.0>Aurora 8B/10B=Srio 2.0.

(3)數據傳輸方式

Aurora 8B/10B協議在數據封裝過程中未添加地址,設備號等信息,不能對目標設備的存儲空間進行讀寫。

PCIe 2.0可通過Memory Write,Memory Read,I/O Write,I/O Read事務對目標設備地址空間進行讀寫,但必須具備對目標設備地址空間的可見性。

SRIO 2.0數據傳輸方式更為靈活。在具備對目標設備地址空間可見性的情況下,可通過NWRITE,NWRITE_R,SWRITE,NREAD,ASTOMIC等事務對目標設備的地址空間進行直接讀寫。在不具備目標設備地址空間可見性的情況下,SRIO還提供了消息傳遞機制。用戶將數據和信箱號通過MESSAGE事務發至目標設備,目標設備根據信箱號與自身存儲空間的映射關系將數據寫入存儲空間。

綜上可知,數據傳輸方式的靈活性上,SRIO 2.0>PCIe 2.0>Aurora 8B/10B.

(4)協議開銷和數據傳輸速率

三種協議均在物理層有20%的8B/10B編碼開銷。Aurora 8B/10B協議除此之外基本上無其它開銷,而PCIe 2.0,SRIO 2.0還存在數據包開銷。與PCIe 2.0相比,SRIO 2.0的數據包格式更為簡潔,在相同的包載荷大小下,開銷更低。以256B包載荷為例,SRIO 2.0的數據包開銷最低為5.4%(SWRITE事務),而PCIe 2.0的數據包開銷最低為7.3%(Memory Write事務)。然而,PCIe 2.0協議最大允許的包載荷為4KB,而SRIO最大允許的包載荷為256B.故PCIe 2.0協議可通過增大包載荷來達到更低的數據包開銷。(4KB包載荷下,PCIe 2.0的數據包開銷為0.5%)

協議的理論傳輸速率由通道帶寬和協議開銷決定,而協議的實際傳輸速率還受設備本身性能的影響。本測試中,PCIe 2.0 DMA讀操作數據傳輸速率速率高于SRIO 2.0 NREAD的主要原因是服務器對FPGA的PCIe讀請求的響應要快于DSP對FPGA的SRIO讀請求響應。

(5)設備尋址

PCIe協議中,各設備共享一個PCIe地址空間。整個PCIe地址空間先被分成塊,根據后來的下級總線這些塊再進一步劃分。樹形結構中的每個設備在整個地址空間映射中被指定一個地址空間,通過執行全部地址譯碼來查找設備。在支持帶有大容量存儲器的設備系統中,這種設備尋址機制不適合靈活拓展。

SRIO采用基于設備ID尋址的方案。采用該方案,使得拓撲結構的變化僅需要更新事務路徑中的設備,從而使系統的拓展與拓撲結構的更改比PCIe協議更為靈活。

Aurora 8B/10B協議未定義設備尋址機制。

(6)網絡拓撲

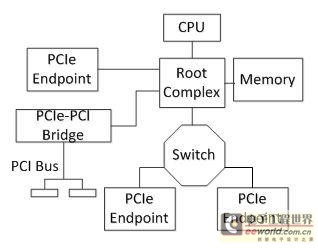

PCIe規定了生成樹拓撲結構,這種結構適合于單個主機,多個外圍設備通信模式,但限制了端點數量,且不支持任意節點與節點間直接通信。PCIe的典型網絡拓撲結構如圖15所示。

圖15 PCIe網絡拓撲結構

SRIO的拓撲結構比PCIe更為靈活,可設計成網型,星型,雛菊鏈或樹形拓撲結構,支持節點對節點通信,各節點間可對等的發起數據傳輸。

Aurora 8B/10B協議不支持網絡拓撲結構。

(7)應用領域

Aurora 8B/10B協議作為Xilinx公司開發的輕量級鏈路層協議,協議開銷小,鏈路數目和鏈路線速率選擇靈活,適用于兩片Xilinx FPGA之間的數據流傳輸。用戶也可在其基礎上開發高層協議。但其應用范圍較為有限,尚未見在其他芯片中使用。

PCIe 2.0作為PCI總線的繼承,帶寬,拓展靈活性大大提高,適合于主機與外部設備的互聯,在PC/Server平臺、VPX平臺有廣泛應用,如聲卡、顯示卡、網絡設備(包括以太網、Modem)、光纖接口卡、磁盤陣列卡等。

SRIO 2.0作為一種高性能包交換的互連技術,數據傳輸方式和拓撲結構靈活,為多處理器系統的實現提供便利,廣泛用于嵌入式系統內的微處理器、DSP、通信和網絡處理器、系統存儲器之間的高速數據傳輸。

7結束語

本文基于Virtex-6 FPGA芯片,對Aurora 8B/10B,PCIe2.0,SRIO 2.0三種串行通信協議進行了速率測試,并通過分析協議開銷和協議的流控制機制,計算了三種協議的理論傳輸速率和協議實際通信效率。結合測試結果和三種協議的具體內容,對三種協議的相關參數和應用領域進行了對比分析。本文測試模塊結構的設計可為三種協議的工程實現提供借鑒,協議實際傳輸速率的測算和協議理論傳輸速率的分析計算可為三種協議在不同平臺和工作模式下的測試提供參考。在進行雷達信號處理機數據傳輸方案的設計時,可參照本文對三種協議的性能分析,根據系統自身的特點及對數據傳輸速率的要求,合理選擇協議類型和協議的工作模式。

評論