微處理器和多處理器片上系統(tǒng)MPSOC設(shè)計的新紀(jì)元

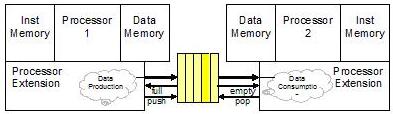

圖 7: 硬件數(shù)據(jù)隊列機制

數(shù)據(jù)隊列對任務(wù)間的性能有一定的影響。如果數(shù)據(jù)隊列生產(chǎn)者和消費者速率高度一致,那么隊列長度可以比較短。如果隊列生產(chǎn)者或者消費者速率不同,那么需要設(shè)計深度隊列來彌補二者之間的失配。

由于處理器執(zhí)行部件的隊列接口對商用處理器核而言具有極其重要的特性,因此更加深入地對接口機制進行一些探討是非常必要的。數(shù)據(jù)隊列接口通過如下TIE語法格式添加到Xtensa LX處理器中:

queue in|out

上面語法格式定義了數(shù)據(jù)隊列的名稱、寬度和隊列的方向。一個Xtensa LX處理器可以包含300多個隊列,每個隊列寬度可以高達1024位。設(shè)計人員可以采用數(shù)據(jù)隊列來對處理器性能進行折中,即在快速、窄帶處理器接口和慢速、寬帶接口之間進行折中以獲得系統(tǒng)高帶寬和高性能的目的。

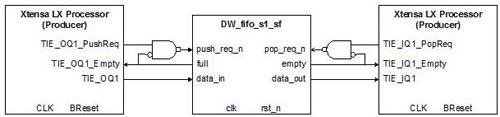

圖8為TIE隊列和簡單的Designware FIFO隊列之間的連接,這種連接方式非常容易。TIE隊列的push 和 pop操作由FIFO的隊列空和隊列滿狀態(tài)信號進行門控,這樣可以使設(shè)計與Designware的 FIFO控制模式保持一致。

圖8:采用TIE隊列的Designware同步FIFO示意圖 (diag_n輸入驅(qū)動為高且almost_full、 half_full、almost_empty和 error輸出均未用)

TIE隊列可以和寄存器操作數(shù)、系統(tǒng)狀態(tài)或者存儲器接口那樣直接為TIE指令提供輸入和輸出操作數(shù)。下面的TIE語法格式建立了一條新的指令,該指令對輸入數(shù)據(jù)隊列中的數(shù)據(jù)進行累加,然后送給寄存器文件。

operation QACC {inout AR ACC} {in IQ1} {

assign ACC = ACC + IQ1;

}

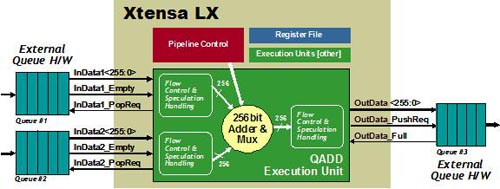

圖9表示TIE隊列是如何像其它指令操作數(shù)那樣在Xtensa LX處理器中使用的。

圖9:TIE隊列作為指令操作數(shù)使用

Xtensa LX處理器本身包括一個兩項的數(shù)據(jù)緩沖器,用于緩沖系統(tǒng)設(shè)計人員定義的每個TIE隊列。每個隊列的兩項數(shù)據(jù)緩沖器所占用的面積大大小于一個加載/存儲處理單元。因此,TIE隊列接口所占的處理器面積是完全受到設(shè)計人員所控制的,并且可以按照需要增大或者減小。

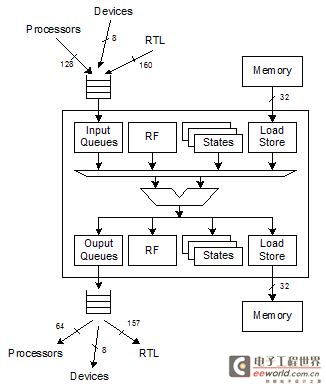

數(shù)據(jù)流直達處理

數(shù)據(jù)端口和數(shù)據(jù)隊列與可配置處理器執(zhí)行部件直接相連,這種互連允許處理器應(yīng)用數(shù)據(jù)流直達技術(shù)進行處理,而那些應(yīng)用在以前是為手工編寫的RTL代碼邏輯塊預(yù)留的。將數(shù)據(jù)隊列和輸出隊列接口與設(shè)計人員定義的執(zhí)行部件相結(jié)合就可以建立一個在處理器內(nèi)部由固件控制的處理模塊,該模塊可以從輸入數(shù)據(jù)隊列中讀取數(shù)據(jù),對這些數(shù)據(jù)執(zhí)行計算,然后按照流水線方式每完成一個“輸入-計算-輸出”周期就將計算結(jié)果輸出。圖10表示一個簡單的系統(tǒng)設(shè)計,該系統(tǒng)有兩個256位的輸入數(shù)據(jù)隊列,一個256位的輸出數(shù)據(jù)隊列和一個256位的加法器/多路器執(zhí)行部件。盡管該處理器擴展是在固件模式下進行控制的,但是其操作可以將處理器的存儲器總線和加載/存儲單元旁路以便可以獲得同硬件一樣的處理速度。

圖10:通過在可配置處理器中增加數(shù)據(jù)流直達處理模式來將執(zhí)行部件和多個隊列相結(jié)合

即使在處理器擴展中使用大量的硬件,但在定義時也只是僅僅寫如下四行TIE代碼而已:

queue InData1 256 in

queue InData2 256 in

queue OutData 256 out

operation QADD {} { in InData1, in InData2, in SumCtrl, out OutData} { assign OutData = SumCtrl ? (InData1 + InData2) : InData1; }

前三行代碼定義了一個256位的輸入隊列和一個256位的輸出隊列,第四行定義了一條新的處理器指令QADD,該指令執(zhí)行256位的加法運算或者將256位的數(shù)據(jù)從輸入隊列送到輸出隊列。通過TIE語言定義的指令告訴Xtensa處理器產(chǎn)生器自動為處理器增加相應(yīng)的硬件,同時為處理器軟件開發(fā)工具增添一條新指令。

用于多處理器片上系統(tǒng)MPSOC設(shè)計的處理器核

可配置處理器的出現(xiàn)使得片上系統(tǒng)SOC設(shè)計人員可以建立起一種嶄新的且非常靈活的硬件模塊構(gòu)建方法。同傳統(tǒng)的固定指令集體系結(jié)構(gòu)ISA處理器相比,可配置處理器通過添加用戶定制的執(zhí)行功能部件、寄存器和寄存器堆以及專用通信接口能夠獲得很高的系統(tǒng)性能。

自從1971年第一個微處理器研制成功至今已經(jīng)30多年,由于受固定處理器核的束縛,導(dǎo)致可配置處理器的發(fā)明無法實現(xiàn)。對于二十一世紀(jì)的片上系統(tǒng)SOC設(shè)計而言,這些制約因素已經(jīng)不再存在,而且這些過時的約束也不再限制系統(tǒng)設(shè)計人員對處理器的使用。

評論