如何選擇正確的芯片驗證方法

一個項目中需要使用的工具和技術必須在設計周期的初期就確定下來,以便獲得新驗證方法費用預算的準確信息。經常有公司因為錯誤估計了運轉這些新型工具和技術所需的設計和技術的復雜性而浪費大量的資金和資源。

產品的抽象級越高,越容易設計;同樣的,抽象級越高,越容易犯嚴重的錯誤。一個架構上的缺陷可能會導致整個芯片的損害,而在門級網表中的連線錯誤可以通過重制解決。

例如,Verilog為設計者提供了一種相對容易的接口,以便他們在相當抽象的層次上進行設計。當設計曾經作為制約性的瓶頸時,Verilog 為設計生產率帶來了指數增長,并且大大推動了復雜芯片的發展。但是如果設計者不了解在復雜的設計周期中語言上的細微差別,就很容易犯錯。在驗證成為瓶頸的今天,同樣的觀點也適用于許多驗證技術和語言。

本文將對時下流行的驗證技術(形式驗證、隨機、定向、有約束的隨機、斷言、屬性檢驗)與語言(SystemC、C/C++、SystemVerilog、Open-VERA、E等)進行全面評述,還將分析在傳統的數字ASIC設計流程中應當在何時采用何種驗證技術和語言。

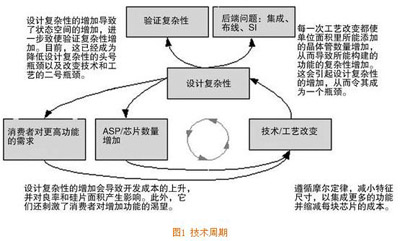

1 驗證瓶頸

盡管事實表明如今設計生產率的增長速度仍然低于芯片復雜度的增長速度,然而現在需要面對的瓶頸已不再是設計時間,而是驗證時間。最近的統計數據表明,對一個復雜邏輯芯片而言,整個產品周期中 60_70% 的時間都用于驗證工作。如何使用新的工具和技術對設計中的復雜功能進行驗證已經成為縮短總體的產品時間所需要面對的挑戰。

由于以下原因,可以說驗證瓶頸在某種程度上是設計抽象級逐步提高造成的結果:

1) 在較高的抽象水平上進行設計,易于構建高度復雜的產品功能。設計復雜度的提高造成驗證工作的成倍增加;

2) 在設計、轉換以及映射到最終產品的過程中,應用更高的抽象級進行設計會帶來信息損失和解釋錯誤的問題。例如,采用HDL級設計并將其轉換到門級的綜合過程,需要進行驗證以確保轉換的正確性以及使設計意圖完全得到體現。提高抽象級還帶來了代碼解釋問題,在仿真時要通過這些代碼對設計進行描述,以確保所寫的代碼真實反映了功能規范。

其它影響驗證問題的因素還包括:

1) 由于設計中硬件與軟件、模擬與數字等共存而造成的功能復雜度增加;

2) 對系統可靠性的要求增高,使得對驗證工作的要求也增加,以確保在系統環境下,芯片功能可以順利執行。

統計數據表明,驗證問題現實存在,而且讓公司付出了高昂的成本:

1)由于設計錯誤造成的芯片缺陷:在需要進行重制的芯片中,有82%是由于邏輯與功能缺陷設計錯誤。這意味著驗證過程沒有覆蓋邊角情況,缺陷一直隱藏在設計過程中直到流片。

2)由于規范錯誤造成的芯片缺陷:在需要進行重制的芯片中,有47%是由于邏輯與功能規范不正確或不完整,有32%是由于規范發生了改變。

3)重用IP和外來IP的問題:所有失敗的芯片中,有14%是由于在重用或外來的IP中存在錯誤。

4)重制的后果:重制費會高達10萬美元,還會延誤產品的推出,由于使用這些有缺陷的芯片而導致的系統失敗也會增加成本。

為了提高驗證生產率,EDA行業提出了一個與解決設計瓶頸類似的解決方案——抽象化的理念。諸如 Verilog 和VHDL等高層次的語言被用于驗證芯片,這些語言包括各種指令如任務指令和線程指令(fork/join 語句),以及控制結構(while語句)。這提供了更強的數據控制力,以便對所有邊角設計進行充分驗證。然而,這些指令不能被綜合,因此不會被用作實際設計代碼的一部分。

隨著復雜度與日俱增,能夠驗證具有不同抽象級的復雜設計的新語言被創建出來,支持這些新的驗證語言的技術和工具也隨之誕生。

所有這一切意味著芯片廠商必須對新的工具作出評估,必須針對這些新的工具和技術對工程師進行培訓,在公司的研發費用成本結構中必須包括新的工具和資源,公司在總體上必須在短時間內克服學習曲線問題,另外,還需要對這些工具進行風險評估,以及考慮新工具與已有技術的集成和協同工作的能力。

2 驗證與確認(Validation)

除了驗證問題之外,芯片公司還要面對確認時間問題。Kropf將“確認”定義為“通過檢查實現行為以獲得對規范的信心的過程”。在驗證和確認之間,有一種觀點認為,“確認能夠確保這是正確的設計,而驗證則是確保這個設計是正確的”;另外一種觀點認為,“驗證指硅片成為成品之前的測試(Verilog/VHDL 仿真等),確認指硅片成為成品之后的測試(在實驗室里測試電路板上的芯片)”。

無論是確認還是驗證,若要保證硅片滿足規范要求,要完成以下兩個步驟:1)通過文件或建模,芯片規范得到了正確的解釋;2)以上解釋得到了正確的理解與實現(一般是通過 HDL),綜合入硅片,并封裝成為芯片。

本文認為第二步是驗證,第一步是確認。目前業界流行的設計流程如圖1所示,此流程可保證以上兩個步驟的要求得以滿足。根據待實現功能的復雜程度不同,可以跳過一些步驟或者增加一些步驟。例如,如果某一項設計是純粹面向硬件的,不涉及驅動或軟件,那么可以從抽象級3直接跳到抽象級1,鎖相環設計即為一例。

當設計按照抽象級逐步推進時,要注意必須一直保持等效性,以確保最低層的抽象級能滿足系統規范的要求。例如:

1)當 C 模型被置于一個系統環境并能夠滿足規范中所描述的所有系統要求時,芯片規范(一般是一個文本文件)與其 C 模型之間就達到了等效。這在實質上是功能等效。

2)通過比較 C 模型與HDL 實現的輸出,可以在規范的C 模型與其 HDL 實現之間建立等效關系。在沒有 C 模型的情況下,可使用“期望數據模型”。這在實質上也是功能等效。

3)HDL實現與門級(綜合后的)之間通過應用“邏輯等效性檢驗”可以建立等效關系。這時,由于設計采取的形式是純粹的邏輯門,而且功能能夠被表示為邏輯表達式,因此,這在實質上是邏輯等效。

評論