MSP430F5529 (三)統一時鐘系統UCS-2

/*1.配置IO口5.4和5.5為XT1功能。*/

/*2.配置XCAP為XCAP_3,即12PF的電容。*/

/*3.清除XT1OFF標志位。*/

/*4.等待XT1起振。*/

#include <msp430.h>

void main(void){

P1SEL |= BIT0;P1DIR |= BIT0;//測量ACLK用

P2SEL |= BIT2;P2DIR |= BIT2;//測量SMCLK用

P7SEL |= BIT7;P7DIR |= BIT7;//測量MCLK用

P5SEL |= BIT4|BIT5; //配置為XT1功能,電路板上晶振接于這兩腳

UCSCTL6 |= XCAP_3; //配置電容為12pF

UCSCTL6 &= ~XT1OFF; //使能XT1

/*下面是很重要的一步:*/

/* XT1剛剛起振的時候可能有錯誤,導致時鐘錯誤標志位置位,必須先清零*/

/*OFIFG即Osc Fault Flag,位于SFRIFG1中*/

while(SFRIFG1 & OFIFG) //如果有時鐘錯誤{

UCSCTL7 &=~(XT2OFFG+DCOFFG+XT1LFOFFG);//清除3種時鐘錯誤標志

SFRIFG1&=~(OFIFG);//清除時鐘錯誤標志位}

UCSCTL4&=(UCSCTL4&(~(SELS_7|SELM_7)))|SELS_0|SELM_0;

//將SMCLK和MCLK時鐘源配置為XT1}

實驗三:DCO-FLL數控振蕩器結合鎖相環

DCO模塊在MSP430F5529系列芯片中非常重要,因為從MSP430F4XX開始,MSP430引用了FLL模塊,FLL即鎖相環,可以通過倍頻的方式提高系統時鐘頻率,進而提高系統的運行速度。

DCO模塊運行需要參考時鐘REFCLK,REFCLK可以來自REFOCLK、XT1CLK和XT2CLK,通過UCSCTL3的SELREF選擇,默認使用的XT1CLK,但如果XT1CLK不可用則使用REFOCLK。

DCO模塊有兩個輸出時鐘信號,即DCOCLK和DCOCLKDIV,其中,倍頻計算公式如下:

DCOCLK = D*(N+1)*(REFCLK/n)

DCOCLKDIV = (N+1)*(REFCLK/n)

其中:n即REFCLK輸入時鐘分頻,可以通過UCSCTL3中的FLLCLKDIV設定,默認為1,也就是不分頻;

D可以通過UCSCTL2中的FLLD來設定,默認為1,也就是2分頻;

N可以通過UCSCTL2中的FLLN來設定,默認值為32。

所以,系統上電后如果不做任何設置,DCOCLK的實際值為2097152,DCOCLKDIV的實際值為1048576。

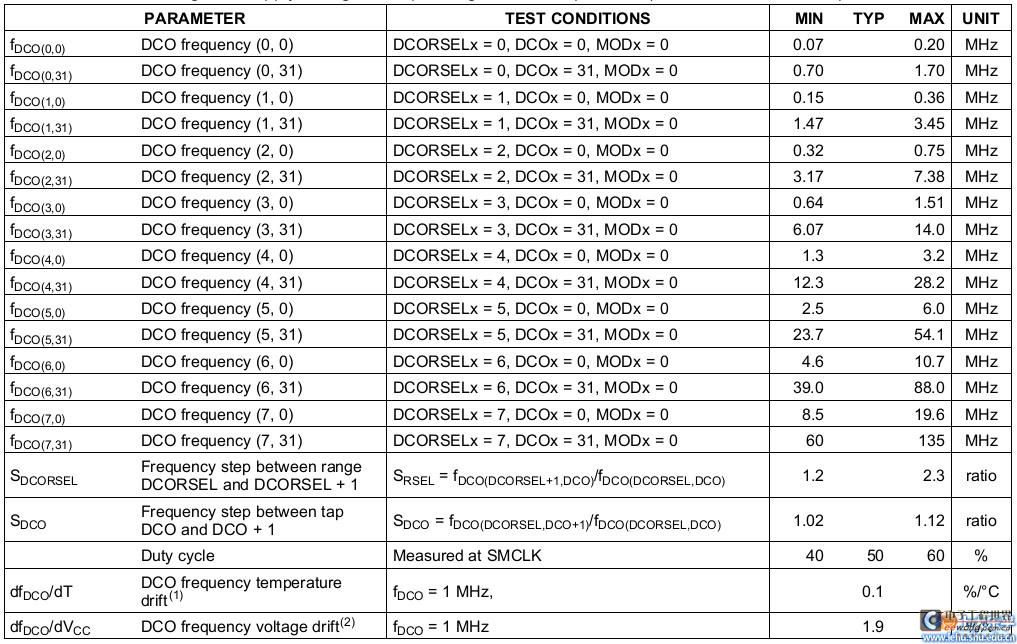

另外,配置芯片工作頻率還需要配置DCORSEL和DCOx,DCORSEL和DCOx的具體作用如下:

DCORSEL位于UCSCTL1,共3位,將DCO分為8個頻率段。

DCOx位于UCSCTL0共5位,將DCORSEL選擇的頻率段分為32個頻率階,每階比前一階高出約8%,該寄存器系統可以自動調整,通常配置為0。

下表給出了相應設置情況下的頻率調節范圍:

/*通過DCO-FLL將32.768KHZ倍頻到25MHZ*/

#include

#include “HAL_PMM.h”

void delay()

{

volatile unsigned int I;

for(I = 0; I != 5000; ++i){_NOP(); }}//延時函數

void main(void) {

WDTCTL = WDTPW+WDTHOLD;

P1SEL &= ~BIT1;

P1DIR |= BIT1;

P1SEL |= BIT0; //ACLK

P1DIR |= BIT0;

P2SEL |= BIT2; //SMCLK

P2DIR |= BIT2;

P7SEL |= BIT7; //MCLK

P7DIR |= BIT7;

P5SEL |= BIT4|BIT5;

UCSCTL6 |= XCAP_3;

UCSCTL6 &= ~XT1OFF;//打開XT1,否則XT1LFOFFG可能報錯

SetVCore(3); //提高Vcore電壓到最高級,以滿足倍頻需求該函數位于HAL_PMM.H中

__bis_SR_register(SCG0);//該語法為固定格式,意為將括號內的變量置位,SCG0與系統工作模式有關,此時MCLK暫停工作

UCSCTL0 = 0; //先清零,FLL運行時,該寄存器系統會自動配置,不用管

UCSCTL1 = DCORSEL_6;

UCSCTL2 = FLLD_1 | 380;//FLLD=1,FLLN=380,則頻率為

2*(380+1)*32.768=24.969MHZ

__bic_SR_register(SCG0);

__delay_cycles(782000);//系統自帶的精確延時,單位us

while (SFRIFG1 & OFIFG) {

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + DCOFFG);

SFRIFG1 &= ~OFIFG;

}

UCSCTL4 = UCSCTL4&(~(SELS_7|SELM_7))|SELS_3|SELM_3;

//選擇DCO作為時鐘源

while(1){

P1OUT ^= BIT1;

delay();

}

}

評論