ARM體系結(jié)構(gòu)研究(一)

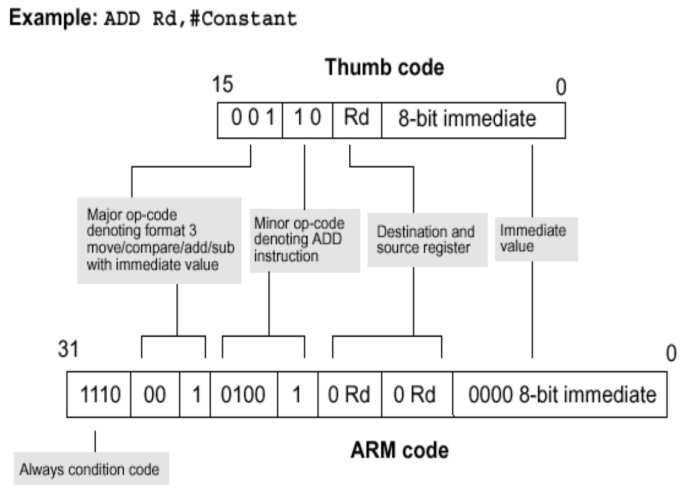

Thumb指令的優(yōu)點(diǎn)在于它可以在保留32位代碼優(yōu)勢的同時(shí),大大節(jié)省系統(tǒng)的存儲(chǔ)空間,因?yàn)樵赥humb指令集中的操作數(shù)仍然是32位的,指令地址也是32位的,只是指令編碼變成了16位,而ARM指令則為32位,所以,相比之下,實(shí)現(xiàn)同樣的功能,Thumb指令的條數(shù)要比ARM略多。圖2.1是“Add Rd,#Constant”在Thumb狀態(tài)和ARM狀態(tài)下的指令比較:

圖2.1 Thumb指令和ARM指令的比較

由上圖我們可以清楚地看到Thumb指令的精簡之處,所以Thumb的存儲(chǔ)空間僅僅是ARM存儲(chǔ)空間的60%~70%,但是Thumb的指令條數(shù)比ARM指令條數(shù)多30%~50%,如果使用32位的存儲(chǔ)器,由于指令條數(shù)較少等原因,ARM指令會(huì)比Thumb指令快40%左右,而使用16位存儲(chǔ)器時(shí),Thumb指令則會(huì)快40%~50%。同時(shí)與ARM比較Thumb指令的功耗會(huì)降低約30%。但是Thumb指令也有其局限性。第一、偏移范圍,在Thumb指令中條件轉(zhuǎn)移偏移只有8位,也就是說只能在256Byte的范圍內(nèi)有條件地轉(zhuǎn)移,在無條件轉(zhuǎn)移中可以有16位的偏移,而這些在ARM指令中都是32位,大大提高了靈活性。同時(shí),在Thumb指令中不支持乘法和累加,沒有協(xié)處理器指令沒有信號(hào)量指令也沒有CPSR指令。

在面臨二者的取舍的時(shí)候,同其它無數(shù)的案例一樣,發(fā)揮各自的長處是最完美的解法。如果系統(tǒng)對性能要求較高,應(yīng)采用32位的存儲(chǔ)器和ARM指令集,而對功耗和成本要求較高,則應(yīng)使用Thumb指令集。但是如果兩者結(jié)合使用,讓它們充分發(fā)揮各自的優(yōu)點(diǎn),則會(huì)取得更好的效果。

ARM指令的基本格式如下:

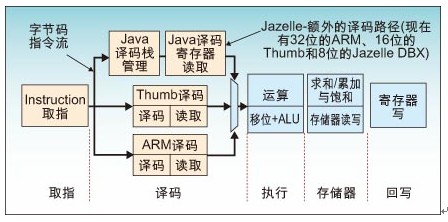

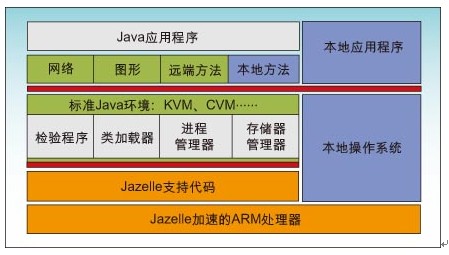

其中<>號(hào)內(nèi)的項(xiàng)是必須的,{}號(hào)內(nèi)的項(xiàng)是可選的,opcode為指令助記符;cond是該動(dòng)作的執(zhí)行條件;S表示影響CPSR寄存器(程序狀態(tài)寄存器)的值,如果不加則表示不影響CPSR的值;Rd表示運(yùn)算結(jié)果的目標(biāo)寄存器;Rn表示第1個(gè)操作數(shù)的寄存器;operand2表示第2個(gè)操作數(shù),可選。 同時(shí),ARM芯片還支持協(xié)處理器,在ARM指令集中有對協(xié)處理器的數(shù)據(jù)操作、數(shù)據(jù)讀取、數(shù)據(jù)寫入和CPU與協(xié)處理器的寄存器傳送的相應(yīng)指令。 ARM指令集詳細(xì)介紹見附錄A。 2.5 運(yùn)行Java虛擬機(jī)(JVM)解釋Java字節(jié)碼這種方式對大多數(shù)嵌入式應(yīng)用來說占用空間過多,運(yùn)行速度過慢。而系統(tǒng)發(fā)展的趨勢及市場的需求決定了Java應(yīng)用需要有更強(qiáng)的圖形處理能力以及一個(gè)強(qiáng)大的Java虛擬機(jī)。于是催生出了Jazelle技術(shù),從硬件上對Java虛擬機(jī)提供支持。 Jazelle DBX(Direct Bytecode eXecution)是一種硬件架構(gòu)擴(kuò)展技術(shù),為ARM處理器引入了第三套指令集—Java字節(jié)碼。新指令集建立了一種新的狀態(tài),處理器在此狀態(tài)下處理Java字節(jié)碼取指令、譯碼和維護(hù)Java操作數(shù)棧等任務(wù)。允許它們在某些架構(gòu)的硬件上加速執(zhí)行Java字節(jié)碼,就如其他執(zhí)行模式般,它能在現(xiàn)存的ARM與Thumb模式之間互相切換。為了降低芯片尺寸并提高性能,Jazelle DBX沒有設(shè)計(jì)成傳統(tǒng)形式的微引擎,而是融入流水線中的一個(gè)有限狀態(tài)機(jī)。如圖2.2所示 Jazelle DBX技術(shù)增加了一條新的“Branch-to-Java”指令來進(jìn)入Java狀態(tài)。此指令支持條件執(zhí)行,先檢查條件標(biāo)志,如果條件滿足,處理器進(jìn)入Java狀態(tài),跳轉(zhuǎn)到指定目標(biāo)地址,開始執(zhí)行Java字節(jié)碼。在Java狀態(tài)下,PC寄存器仍是32位尋址Java字節(jié)代碼。字節(jié)碼的取指、譯碼分別在兩個(gè)流水段完成(對應(yīng)ARM/Thumb狀態(tài)下為一個(gè)譯碼流水級)。32位的取指令操作一次性可以取4個(gè)Java字節(jié)碼,性能優(yōu)勢十分明顯,對于一個(gè)高度優(yōu)化的商業(yè)Java虛擬機(jī),運(yùn)行評測程序或復(fù)雜的MIDP2.0應(yīng)用,Jazelle DBX技術(shù)通常可帶來約2~4倍的性能提升。Jazelle DBX技術(shù)允許所有的Java指令是“可重新開始”的。這樣在執(zhí)行Java指令過程中,即刻響應(yīng)中斷,從而減少中斷延遲,確保實(shí)時(shí)性能。 在ARM處理器的Java狀態(tài)下,有若干個(gè)ARM寄存器可以功能復(fù)用(包括棧指針、棧頂四項(xiàng)(top4 elements of stack)、局部變量0等)。正是這些硬件復(fù)用設(shè)計(jì),才使得只用了很少的額外邏輯(約一萬兩千門)就實(shí)現(xiàn)了一個(gè)Java機(jī)。把所有Jazelle DBX擴(kuò)展所需的狀態(tài)用ARM寄存器保存,也保證了和現(xiàn)有操作系統(tǒng)、中斷處理程序和異常處理代碼的兼容性。把棧頂四項(xiàng)保存在ARM寄存器中也能提高Java性能。大量的程序分析顯示,大多數(shù)程序的棧深度是很小的,所以這項(xiàng)策略可以盡量減少內(nèi)存訪問,硬件也可自動(dòng)處理?xiàng)R绯龌蛳乱纭?p>和Java協(xié)處理器或其它專用Java處理器設(shè)計(jì)不同的是,Jazelle DBX和主處理器共用緩存,這一方面能夠降低功耗,而且還可以提高性能。另一個(gè)重要的設(shè)計(jì)考慮是確保Jazelle DBX技術(shù)不會(huì)影響實(shí)時(shí)中斷性能,仍保持與操作系統(tǒng)中已有ARM異常處理代碼的兼容。圖2.3是在加入了Jazelle的ARM處理器中運(yùn)行Java應(yīng)用的垂直架構(gòu)架圖。 圖2.3加入了Jazelle的ARM處理器上的Java應(yīng)用垂直架構(gòu)圖

評論