淺談ARM架構1

ARM->Thumb:操作數寄存器狀態為1,執行BX指令。

本文引用地址:http://www.104case.com/article/201611/317875.htmThumb->ARM:操作數寄存器狀態為0,執行BX指令。或者是處理器進行異常處理(IRQ,FIQ,Reset,Undef,Abort,SWI ARM狀態執行)時,把pc指針放入異常模式鏈接寄存器中,并從異常向量地址開始執行程序,也可以使得處理器切換到ARM狀態。

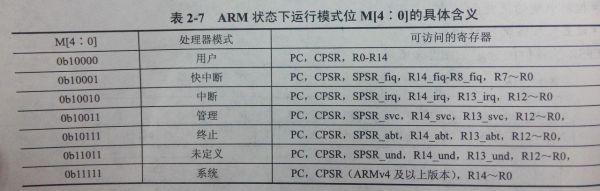

以上是整體指令集系統的情況,接下來說一下ARM處理器的運行模式。用過Linux的都知道,操作系統有很多運行模式,其實著很多的運行模式也是需要處理器支持的。ARM處理器的運行模式有七種:(除用戶模式,別的均屬于非用戶模式或者特權模式;除了用戶模式和系統模式,別的都稱為異常模式)

用戶模式(USR):正常狀態;

快速中斷模式(FIQ):用于高速數據傳輸或通道形式;

外部中斷模式(IRQ):用于通用的中斷處理;

管理模式(SVC):操作系統使用的保護模式;

數據訪問終止模式(ABT):當數據或指令預取終止時進入該模式,可用于虛擬存儲保護及存儲保護;

系統模式(SYS):運行具有特權的操作系統任務;(Linux下就是root用戶了)

未定義指令中斷模式(UNDEF):當未定義的指令時進入該模式,可支持硬件協處理器的軟件仿真。

那么我們為了實現以上的模式,我們在處理器這里資源應該如何分配呢?這里就涉及到寄存器組了。寄存器組就可以存儲這些模式,并在該模式下操作所需要的數據。

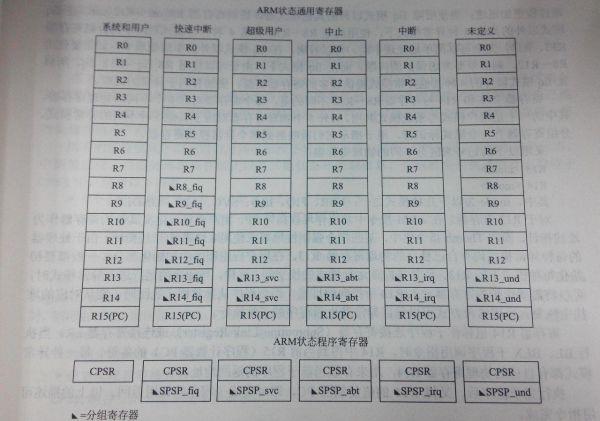

以下就是ARM指令集的寄存器組:

我們可以看到針對一些特定的模式寄存器組會有所改變。一共有37個32bit的寄存器。帶三角形的就是分組寄存器,專用寄存器。快速中斷的7個便于快速中斷。R0~R7是未分組寄存器,通用。

當別的除了快速中斷模式之外,別的模式因為要訪問R8~R12,就有可能在模式轉換的時候要保護現場。

一般來說,R13就是堆棧寄存器,當然指定別的寄存器也是可以的。

R14其實就是子程序鏈接地址,比如遞歸的時候,它里面存的就是返回地址。比如匯編的

MOV PC,LR

BX LR

以上就是實現了返回鏈接地址。另外R14還可以處理中斷或者異常返回。

R15就是程序計數器(PC)。ARM的[31:2]來保存地址,因為是4個字節。Thumb指令集就是[31:1]是地址,[0]=0。因為只有兩個字節,指令之間的地址就是相差2。由于是多級流水線設計,所以保存PC的時候要注意PC會因流水線而改變。

當然上面說了很多模式還有什么狀態恢復,返回之前狀態,堆棧處理啊其實和真正你在寫處理器的時候不用管,因為很多功能是通過調度實現的,不用太在意更高抽象層次的東西。在這里說一下只是增加一些在處理器硬件低層實現之后如果完成那些復雜程序有更多的了解。

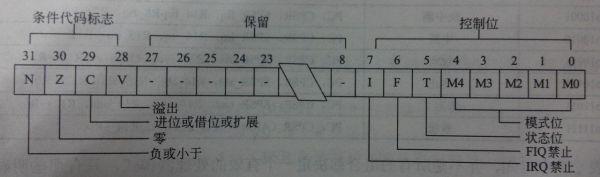

CPSR:也就是程序狀態寄存器。這種寄存器就是存儲整個程序執行的一個狀態。包括了4 bit的條件代碼標志(N,Z,C,V);2bit中斷禁止位(分別用于一種類型的中斷);5bit去對當前處理器操作模式進行編碼的位;1bit用于指示當前執行的是Thumb還是ARM指令集。

如圖:

中斷禁止位:I,F

I = 1,禁止IRQ機制;F = 1,禁止FIQ機制。

T表示標志位,該位反應了處理器的運行狀態。

如果模式不確定,那么就會導致進行復位。

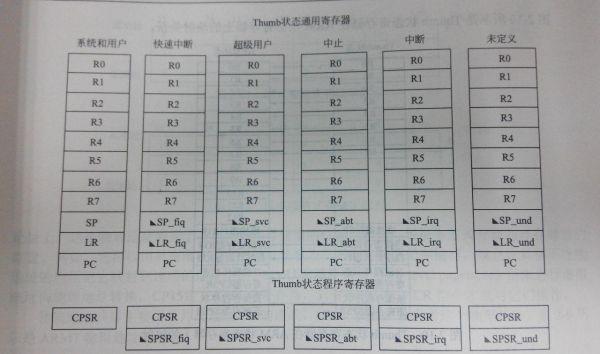

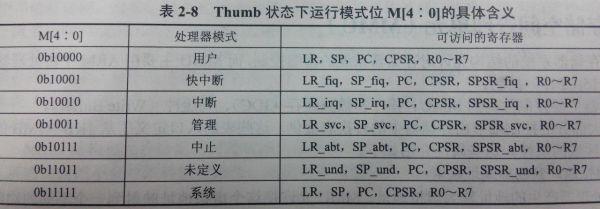

看一下Thumb指令集系統:

thumb指令集系統的模式位的含義:

評論