Xilinx 16nm UltraScale+實現(xiàn)2至5倍的性能功耗比優(yōu)勢

臺積公司的16nm FinFET工藝與賽靈思最新UltraRAM和SmartConnect技術(shù)相結(jié)合,使賽靈思能夠繼續(xù)為市場提供超越摩爾定律的價值優(yōu)勢。

本文引用地址:http://www.104case.com/article/201610/308338.htm賽靈思憑借其28nm 7系列全可編程系列以及率先上市的20nm UltraScale™系列,獲得了領(lǐng)先競爭對手整整一代優(yōu)勢,在此基礎(chǔ)上,賽靈思剛剛又推出了其16nm UltraScale+™系列器件。客戶采用該器件系列構(gòu)建的系統(tǒng)相比采用賽靈思28nm器件所設(shè)計的類似系統(tǒng)的性能功耗比可提升2至5倍。這些性能功耗比優(yōu)勢主要取決于三大方面:采用臺積電公司16FF+(即16nm FinFET Plus)工藝的器件實現(xiàn)方案、賽靈思的片上UltraRAM存儲器以及SmartConnect創(chuàng)新型系統(tǒng)級互聯(lián)-優(yōu)化技術(shù)。

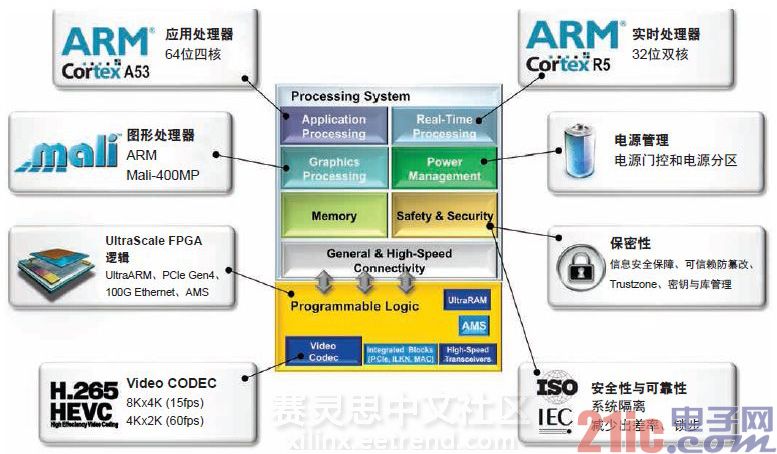

此外,賽靈思還推出了其第二代Zynq®全可編程SoC。Zynq UltraScale多處理SoC (MPSoC) 在單個器件中完美集成了四核64位ARM® Cortex™-A53應(yīng)用處理器、32位ARM Cortex-R5實時處理器、ARM Mali-400MP圖形處理器、16nm FPGA邏輯(帶UltraRAM)、眾多外設(shè)、安全性與可靠性特性、以及創(chuàng)新型電源控制技術(shù)。該新型Zynq UltraScale+ MPSoC為用戶提供了系統(tǒng)創(chuàng)建所需的一切,而且利用其打造出來的系統(tǒng)相比采用28nm Zynq SoC所設(shè)計的系統(tǒng)的性能功耗比提升5倍。

FINFET進一步擴展 ULTRASCALE系列,使其具有額外的節(jié)點價值優(yōu)勢

賽靈思公司芯片產(chǎn)品管理與營銷高級總監(jiān)Dave Myron指出:“采用16nm UltraScale+系列,我們能夠創(chuàng)建出比摩爾定律通常提供給用戶的更高的額外節(jié)點價值優(yōu)勢。我們能滿足LTE Advanced與早期 5G無線、Tb級有線通信、汽車高級駕駛員輔助系統(tǒng)以及工業(yè)物聯(lián)網(wǎng)應(yīng)用等各種下一代應(yīng)用需求。UltraScale+系列使用戶能夠?qū)崿F(xiàn)更大的創(chuàng)新,同時在各自的市場中保持領(lǐng)先競爭對手。”

憑借其UltraScale系列產(chǎn)品,賽靈思能夠同時通過兩個工藝節(jié)點提供器件,即臺積公司的20nm平面工藝(已經(jīng)發(fā)貨)和現(xiàn)在臺積公司的16FF+工藝(賽靈思預(yù)計將于2015年第四季度開始發(fā)貨)。賽靈思將推出16nm UltraScale+系列的Virtex® FPGA與3D IC、Kintex® FPGA以及新型Zynq UltraScale+ MPSoC。

賽靈思公司新產(chǎn)品推出與解決方案市場營銷總監(jiān)Mark Moran表示,賽靈思決定于2013年開始推出其20nm UltraScale系列,而不是等臺積公司的16FF+工藝問世后才發(fā)布。這是因為在一些應(yīng)用領(lǐng)域,早在一年半就迫切需要20nm器件——其比28nm具有更高的性能和容量。

Moran表示:“我們的整個產(chǎn)品系列在設(shè)計時充分考慮到市場需求。采用20nm UltraScale架構(gòu)的器件的功能更適用于那些無需UltraScale+提供的額外性能功耗比優(yōu)勢的市場和最終應(yīng)用中的新一代產(chǎn)品。既然知道16nm緊跟其后,所以我先構(gòu)建了20nm FinFET。同時我們在20nm上進了大量的架構(gòu)修改(我們知道這是16nm的基礎(chǔ)),可以根據(jù)市場需要提高性能和價值水平。我們有客戶已經(jīng)著手在我們目前提供的20nm器件上進行開發(fā),這樣只要16nm Ultra-Scale+器件一問世,他們就可以快速進行設(shè)計移植,進而加速設(shè)計上市進程。”

Myron補充說,眾多Virtex UltraScale+器件會與20nm Virtex Ultra-Scale器件實現(xiàn)引腳兼容,這樣,對需要額外性能功耗比優(yōu)勢的設(shè)計來說易于升級。

Myron說:“從工具角度來說,20nm UltraScale和16nm UltraScale+器件看起來幾乎一樣。因此使用16nm UltraScale+器件還有一大優(yōu)勢,那就是提升性能功耗比使其很容易達到性能和功耗目標(biāo)要求。”

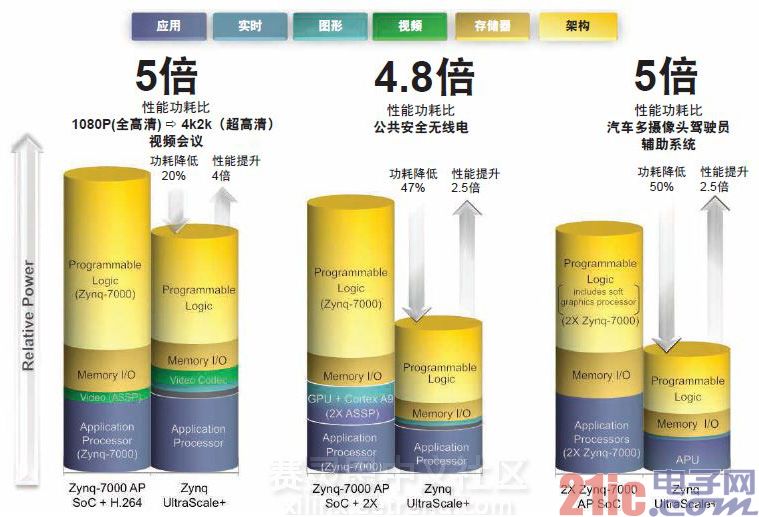

Myron說UltraScale+ FPGA以及3D IC相比28nm 7 系列FPGA,性能功耗比提升2倍。同時,Zynq UltraScale+ MPSoC憑借其額外的集成異構(gòu)處理功能,相比采用28nm Zynq SoC構(gòu)建的類似系統(tǒng),性能功耗比提升5倍(如圖1所示)。

圖1 – 賽靈思16nm UltraScale+ FPGA和Zynq UltraScale+ MPSoC可為設(shè)計團隊提供額外的節(jié)點價值優(yōu)勢。

源于臺積公司16FF+工藝的性能功耗比優(yōu)勢

僅通過向16nm FinFET的工藝移植,賽靈思已推出了比28nm 7 系列器件的性能功耗比高出2倍的器件。Myron指出:“臺積公司的16FF+是一種極其高效的工藝技術(shù),這是因為其基本消除了此前采用平面晶體管實現(xiàn)的芯片工藝相關(guān)的晶體管電源泄漏情況。此外,我們還與臺積公司通力合作,共同優(yōu)化UltraScale+器件,以充分利用該新工藝技術(shù)。至少(僅從該新工藝技術(shù)的創(chuàng)新角度來說),UltraScale+設(shè)計相比采用28nm 7系列器件實現(xiàn)的設(shè)計,性能功耗比提升兩倍以上。

如需了解有關(guān)賽靈思20nm UltraScale架構(gòu),以及FinFET相比平面晶體管工藝的優(yōu)勢的詳細說明,敬請訪問:《賽靈思中國通訊第84期》。

在UltraScale+系列中,賽靈思還將提供業(yè)界首款3D-on-3D器件——其采用臺積公司16FF+ 3D晶體管技術(shù)實現(xiàn)的第三代堆疊硅片互聯(lián)3D IC。

Myron指出,屢獲殊榮的7系列3D IC通過在單個集成芯片上提供多個芯片,突破了摩爾定律的性能和容量極限。

Myron指出:“憑借我們的同質(zhì)3D IC,我們能夠突破摩爾定律的容量極限,從而可提供容量是28nm最大型單芯片F(xiàn)PGA容量2倍的器件。然后利用我們的首款異構(gòu)器件,我們能夠?qū)PGA芯片與高速收發(fā)器芯片組合在一起,提供28nm單芯片器件無法實現(xiàn)的高系統(tǒng)性能與帶寬。利用UltraScale+ 3D IC,我們將繼續(xù)提供超越摩爾定律極限的高容量與性能。”

源于ULTRARAM的性能功耗比優(yōu)勢

Myron說通過采用最新大型片上存儲器UltraRAM,眾多UltraScale+設(shè)計相對28nm將獲得更多的性能功耗比提升。賽靈思將在大部分UltraScale+器件中新增UltraRAM。

Myron指出:“從根本上來說,片上存儲器(如LUT RAM 或分布式RAM和Block RAM)和片外存儲器(DDR或片外SRAM等)之間的差距越來越大。有很多處理器密集型應(yīng)用需要不同類型存儲器。尤其是當(dāng)您設(shè)計更大型更復(fù)雜的設(shè)計時,就更需要較快速的片上存儲器。Block RAM太細太少。而如果您將存儲器放在片外,不僅會增加功耗,讓I/O變得復(fù)雜,而且還會增加材料清單(BOM)成本。

這就是賽靈思開發(fā)UltraRAM的原因。Myron 指出:“我們所做的就是增加片上存儲器分層結(jié)構(gòu)的層數(shù),以及能夠在設(shè)計中輕松實現(xiàn)大型存儲器模塊。我們不僅幫助設(shè)計人員輕松放置恰當(dāng)尺寸的片上存儲器,而且時序也有保障。”

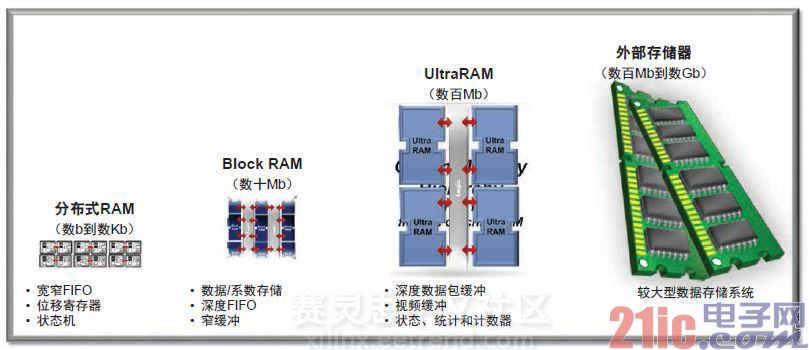

通過LUT或分布式RAM,設(shè)計人員可以添加1b和kb級大小的RAM,而BRAM可讓他們添加10Mb大小的存儲器模塊。UltraRAM允許采用UltraScale+器件的設(shè)計人員用100Mb級的存儲器塊實現(xiàn)片上SRAM(如圖2所示)。這樣做,設(shè)計人員只需較少量的片外RAM (SRAM、RLDRAM和TCAM)就能夠打造出性能/能效更高的系統(tǒng)。同時還會降低材料清單(BOM)成本。最大型的UltraScale+ 器件VU13P具有432 Mb的UltraRAM。

圖2 – UltraRAM可填補片上存儲器和片外存儲器之間的存儲器空白,從而使設(shè)計人員能夠利用較大型的本地存儲器模塊創(chuàng)建性能更高、功耗更低的系統(tǒng)。

源于SmartConnect的性能功耗比優(yōu)勢

另一項新技術(shù)SmartConnect,可進一步提升UltraScale+設(shè)計的性能功耗比優(yōu)勢。

Myron說:“SmartConnect是工具和硬件協(xié)同優(yōu)化的結(jié)晶,也是一種智能方法,即便設(shè)計越來越復(fù)雜,也可輕松實現(xiàn)。”

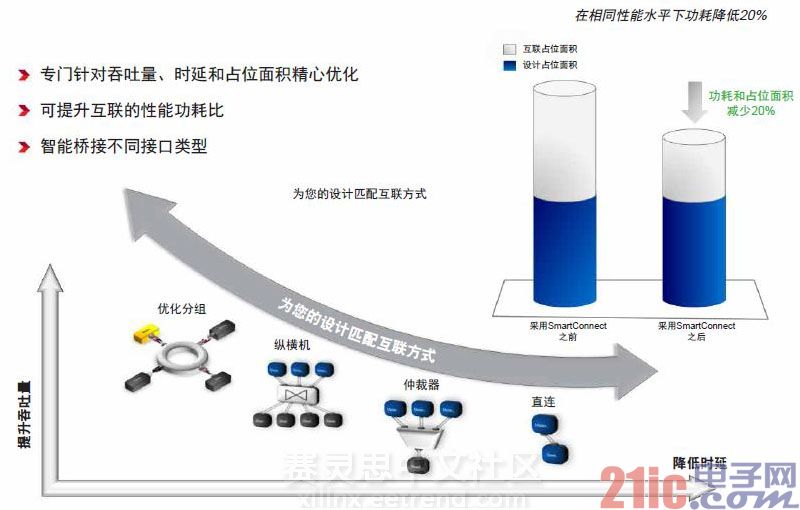

傳統(tǒng)上,當(dāng)工程師在設(shè)計中填充的IP模塊越多,開銷(功耗和占用面積需求)就越大。Myron說借助SmartConnect,賽靈思已向Vivado®設(shè)計套件增加了一些優(yōu)化功能,從而可以從系統(tǒng)級層面考慮整個設(shè)計。SmartConnect具有最有效的互聯(lián)拓撲結(jié)構(gòu),可實現(xiàn)最小的占位面積和最高的性能,從而充分發(fā)揮AXI互聯(lián)的一些最新增強功能以及16nm UltraScale+芯片的優(yōu)勢。

Myron指出:“16nm UltraScale+器件在這個更高的協(xié)議層而不僅僅是在路由層上具有更高的效率。這意味著在16nm FinFET優(yōu)勢的基礎(chǔ)上進一步提高性能功耗比優(yōu)勢。”

圖3展示了一個真實的設(shè)計,其含有8個視頻處理引擎,所有這些引擎均與處理器和儲存器相連。Myron說:也許奇怪,像這樣的一個真實世界的設(shè)計,互連邏輯竟然差不多占用了設(shè)計總面積的一半。這不僅影響功耗,而且還會限制頻率。而SmartConnect可以自動重組互連模塊并在不影響性能的情況下將功耗降低20%。

16nm ULTRASCALE FPGA標(biāo)準(zhǔn)測試

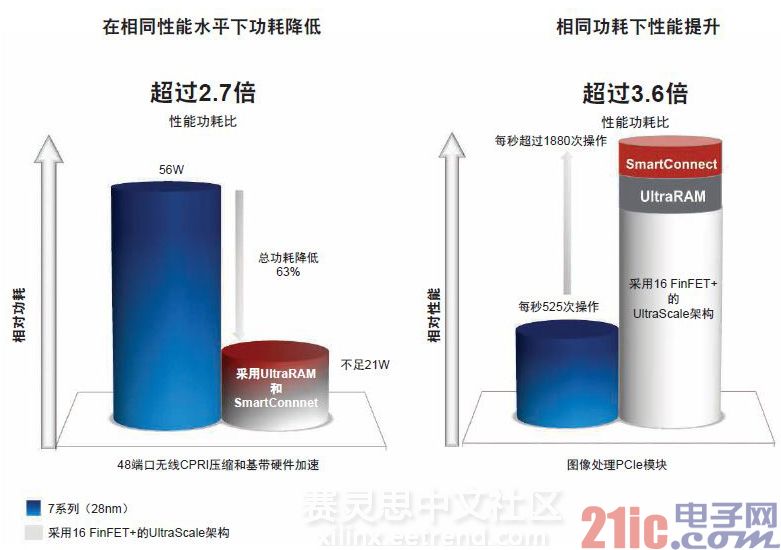

舉例說明FPGA設(shè)計方案的性能功耗比優(yōu)勢,在28nm Virtex-7 FPGA中實現(xiàn)的48端口無線CPRI壓縮與基帶硬件加速器的功耗為56W(如圖4)。在同一性能水平下運行的同一設(shè)計實現(xiàn)在16nmVirtex UltraScale+ FPGA中,功耗僅為27W,相比28nm設(shè)計功耗降低了55%,性能功耗比提升了2.1倍。加上UltraRAM和SmartConnect提供的額外性能功耗比優(yōu)勢,實現(xiàn)在VirtexUltraScale+中的設(shè)計相比28 nm Virtex-7 FPGA實現(xiàn)方案,性能功耗比提升了2.7倍,功耗降低了63%。

同樣,在FPGA功耗預(yù)算為15W的圖像處理PCI模塊中,28 nmVirtex-7可實現(xiàn)每秒525次操作的性能。相比之下,實現(xiàn)在16 nm UltraScale中的同一設(shè)計則可實現(xiàn)每秒1255次操作的高性能,性能功耗比提升了2.4倍。加上UltraRAM和SmartConnect提供的額外性能功耗比優(yōu)勢,Virtex UltraScale +實現(xiàn)方案相比28 nm Virtex-7 FPGA實現(xiàn)方案,性能功耗飆升3.6倍。

圖3 – SmartConnect技術(shù)將互聯(lián)所占用的面積削減達20%,這樣在相同性能水平下,功耗可降低20%。

圖4 – 16nm UltraScale+可為那些設(shè)法在相同功耗預(yù)算范圍內(nèi)更快速實現(xiàn)設(shè)計以及試圖在相同性能水平下大幅降低功耗的設(shè)計人員保持其顯著的性能功耗比優(yōu)勢

ZYNQ ULTRASCALE MPSOC可提供超過5倍的性能功耗比優(yōu)勢

盡管賽靈思原本可以采用臺積公司20 nm工藝實現(xiàn)其第二代全可編程SoC,但公司仍會選擇等待采用臺積公司的16 nm FinFET工藝來實現(xiàn)該器件。該器件的異構(gòu)多處理特性集結(jié)合16nm UltraScale架構(gòu)的性能功耗比優(yōu)勢,可以將16nm Zynq UltraScale+ MPSoC打造成更高效的中央處理系統(tǒng)控制器。該器件可提供超過28 nm Zynq SoC 5倍的性能。

去年,賽靈思針對UltraScale MPSoC架構(gòu)推出了其“為合適任務(wù)提供合適引擎”的使用模型,但保留了有關(guān)Zynq UltraScale+MPSoC器件應(yīng)有的特定內(nèi)核的細節(jié)。目前公司正發(fā)布全特性集Zynq UltraScale+ MPSoC(如圖5所示)。

圖5 – 16nm Zynq UltraScale+ MPSoC采用了一組豐富的處理引擎,設(shè)計團隊能夠為各項任務(wù)量身定制處理引擎,從而實現(xiàn)無與倫比的系統(tǒng)性能,進而顯著提升其系統(tǒng)價值。

當(dāng)然,初始28nm Zynq SoC的最大增值是在單個器件中完美集成了ARM處理系統(tǒng)和可編程邏輯。 Zynq SoC的處理系統(tǒng)(PS)和可編程邏輯(PL)模塊通過超過3000多個互聯(lián)(峰值帶寬運行速率約為84 Gbps)連接在一起。PS和PL之間的緊密相連所提供的吞吐量和性能不是一個包含F(xiàn)PGA和獨立ASSP的雙芯片系統(tǒng)架構(gòu)能簡簡單單實現(xiàn)的。

目前借助16nm UltraScale+ MPSoC,賽靈思顯著提高了處理系統(tǒng)和可編程邏輯之間的性能,為器件提供了超過6,000次互聯(lián)(峰值帶寬運行速率為500Gbps)。賽靈思公司全可編程SoC產(chǎn)品市場營銷與管理總監(jiān)Barrie Mullins指出:“這使得Zynq UltraScale+ MPSoC處理系統(tǒng)與邏輯系統(tǒng)之間的連接速率比采用28nm Zynq SoC可能實現(xiàn)的連接速率快6倍。而且雙芯片(ASSP +FPGA)架構(gòu)的系統(tǒng)性能遠遠落后于此。”

Mullins說Zynq UltraScale+ MPSoC的核心是64位四核ARM Cortex-A53處理器,其可提供2倍于28nmZynq SoC的雙核Cortex-A9處理系統(tǒng)的性能。應(yīng)用處理系統(tǒng)具有硬件虛擬化和非對稱處理功能,可全面支持ARM的TrustZone®套件的安全特性。

賽靈思還為Zynq UltraScale+MPSoC提供了一個雙核ARM Cortex-R5實時處理子系統(tǒng),可幫助用戶向其系統(tǒng)添加確定性操作。實時處理器可確保為需要最高級別吞吐量、安全性和可靠性的應(yīng)用提供即時系統(tǒng)響應(yīng)。

為進一步提升處理性能,Zynq UltraScale+ MPSoC還內(nèi)置了一系列的專用圖形引擎。ARM Mali™-400MP專用圖形加速內(nèi)核可幫助主CPU分擔(dān)圖形密集型任務(wù)。為協(xié)助GPU,賽靈思向用于視頻壓縮/解壓縮(支持8Kx4K (15fps)和4Kx2K (60fps)的H.265視頻標(biāo)準(zhǔn))的可編程邏輯塊添加了一個硬化的視頻編解碼器內(nèi)核。DisplayPort源內(nèi)核可幫助用戶加速視頻數(shù)據(jù)分組,同時還避免其系統(tǒng)使用外部DisplayPort TX發(fā)送器芯片。

Zynq UltraScale+ MPSoC還具有一系列片上存儲器增強功能。該產(chǎn)品系列中的最大型器件,其可編程邏輯中除Block RAM外,還包含UltraRAM。同時Zynq UltraScale+ MPSoC的處理內(nèi)核共享L1和L2高速緩存。

Zynq UltraScale+ MPSoC還采用具備ECC功能的位數(shù)更寬的72位DDR接口內(nèi)核(64位+ECC的8位)。該接口能提供用于DDR4的2,400Mbps速率,可支持32GB容量的更大內(nèi)存深度DRAM。

Zynq UltraScale+ MPSoC上的專用安全單元可提供軍事級安全性,諸如安全啟動、密鑰與庫管理,以及防纂改功能等——這些都是設(shè)備間通信以及互聯(lián)控制應(yīng)用的標(biāo)準(zhǔn)需求。此外,Zynq UltraScale+MPSoC的可編程邏輯系統(tǒng)還采用了針對150G Interlaken、100GEthernet MAC和PCIe® Gen4的集成連接功能塊。板載模擬混合信號(AMS) 內(nèi)核有助于設(shè)計團隊利用系統(tǒng)監(jiān)控器(System Monitor)測試其系統(tǒng)。

借助所有這些功能,不是任何應(yīng)用都會用到MPSoC中的每個引擎。因此,賽靈思為Zynq UltraScale+MPSoC提供了一個極其靈活的專用電源管理單元(PMU)。該內(nèi)核使用戶能夠控制電源域和分區(qū)(粗/細精度),僅為系統(tǒng)正使用的處理單元供電。而且,設(shè)計團隊能夠?qū)υ搩?nèi)核進行編程,以實現(xiàn)動態(tài)操作,從而確保系統(tǒng)僅運行執(zhí)行給定任務(wù)所需的功能,進而降低功耗。PMU還可實現(xiàn)眾多安全性和可靠性,比如信號和誤差的檢測與緩解、安全狀態(tài)模式,以及系統(tǒng)隔離與保護。

Myron表示,歸功于上述探討的16nm新增的所有這些處理功能,采用Zynq Ultra-Scale+ MPSoC構(gòu)建的設(shè)計相比采用28nm Zynq SoC實現(xiàn)的設(shè)計,性能功耗比優(yōu)勢平均提升5倍。

16nm ZYNQ ULTRASCALEMPSOC測試標(biāo)準(zhǔn)

為了說明Zynq UltraScale+ MPSoC的性能功耗比優(yōu)勢,讓我們來看一下該器件服務(wù)的眾多應(yīng)用中的3個應(yīng)用的標(biāo)準(zhǔn)測試結(jié)果,不同顏色用于演示處理引擎的多樣性(如圖6所示)。

圖6 – Zynq UltraScale+ MPSoC擁有豐富的處理模塊、外設(shè)集和16nm邏輯塊,可幫助設(shè)計團隊創(chuàng)建出比采用28nm Zynq SoC實現(xiàn)的設(shè)計高出5倍性能功耗比優(yōu)勢的創(chuàng)新型系統(tǒng)。

為創(chuàng)建一個運行全1080p視頻的視頻會議系統(tǒng),設(shè)計人員采用一個帶有獨立H.264 ASSP的Zynq SoC。利用Zynq UltraScale+ MPSoC的優(yōu)勢,設(shè)計人員現(xiàn)在能夠在單個Zynq UltraScale+ MPSoC中實現(xiàn)4Kx2K UHD系統(tǒng),而且在相同功耗預(yù)算條件下,該系統(tǒng)相比雙芯片系統(tǒng)而言,性能功耗比提高了5倍。

賽靈思公司高級SoC產(chǎn)品線經(jīng)理Sumit Shah表示:“在需求使用Zynq SoC和兩個ASSP的公共安全無線電應(yīng)用中,現(xiàn)在您只需使用一個Zynq UltraScale+ MPSoC就可實現(xiàn)整個設(shè)計,而且相對此前的配置,系統(tǒng)功耗降低了47%,性能提升了2.5倍,從而實現(xiàn)了4.8倍的性能功耗比優(yōu)勢。”

Shah說,同樣的,此前實現(xiàn)在兩個28nm Zynq SoC上的汽車多攝像頭駕駛員輔助系統(tǒng),現(xiàn)在可以縮小到一個Zynq UltraScale+ MPSoC上。單芯片系統(tǒng)比雙芯片設(shè)計的性能提升2.5倍,功耗降低50%。相對此前實現(xiàn)方案而言,這可將性能功耗比凈提升5倍。

針對所有UltraScale Plus產(chǎn)品系列的早期客戶參與計劃正在如火如荼進行。首個流片和設(shè)計工具的早期試用版本預(yù)計將于2015年第二季度推出。公司有望在2015年第四季度開始向客戶出貨UltraScale+器件。

評論