基于ADS的C波段的低噪聲放大器仿真設(shè)計(jì)研究

摘要:低噪聲放大器是接收機(jī)中最重要的模塊之一,文中采用了低噪聲、較高關(guān)聯(lián)增益、PHEMT技術(shù)設(shè)計(jì)的ATF35176晶體管,設(shè)計(jì)了一種應(yīng)用于5.5~6.5 GHz頻段的低噪聲放大器。為了獲得較高的增益,該電路采用三級(jí)級(jí)聯(lián)放大結(jié)構(gòu)形式,并通過(guò)ADS軟件對(duì)電路的增益、噪聲系數(shù)、駐波比、穩(wěn)定系數(shù)等特性進(jìn)行了研究設(shè)計(jì),最終得到LNA在該頻段內(nèi)增益大于32.8 dB,噪聲小于1.5 dB,輸入輸出駐波比小于2,達(dá)到設(shè)計(jì)指標(biāo)。

關(guān)鍵詞:低噪聲放大器;ADS;PHEMT;負(fù)反饋網(wǎng)絡(luò);匹配電路

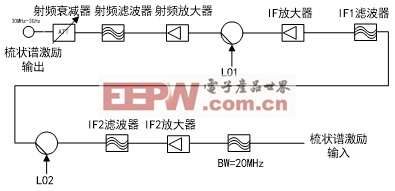

在整個(gè)接收系統(tǒng)中,低噪聲放大器總是處于前端的位置。整個(gè)接收系統(tǒng)的噪聲取決于低噪聲放大器的噪聲。與普通放大器相比,低噪聲放大器一方面可以減小系統(tǒng)的雜波干擾,提高系統(tǒng)的靈敏度;另一方面放大系統(tǒng)的信號(hào),保證系統(tǒng)工作的正常運(yùn)行。總之,低噪聲放大器的性能不僅制約了整個(gè)接收系統(tǒng)的性能,而且,對(duì)于整個(gè)接收系統(tǒng)技術(shù)水平的提高,也起了決定性的作用。

1 低噪聲放大器的設(shè)計(jì)指標(biāo)

低噪聲放大器的主要性能指標(biāo)包括:穩(wěn)定性、功率增益、噪聲系數(shù)、增益平坦度等,在這些指標(biāo)之中噪聲系數(shù)和放大增益對(duì)系統(tǒng)性能的影響較大。因此對(duì)低噪聲放大器的設(shè)計(jì)主要從穩(wěn)定性、功率增益、噪聲系數(shù)、輸入輸出電壓駐波比等方面進(jìn)行考慮。

1.1 穩(wěn)定性

放大器電路必須滿足的首要條件之一是其在工作頻段內(nèi)的穩(wěn)定性。因?yàn)榧偃缭谠O(shè)計(jì)和制造放大器時(shí)不謹(jǐn)慎從事,在微波頻率上一些不可避免的寄生因素往往足以引起振蕩。

所以為了保證電路的穩(wěn)定性,主要采取以下措施:1)可以在源極引入負(fù)反饋,使電路處于穩(wěn)定狀態(tài);2)采用鐵氧體隔離器能穩(wěn)定電路;3)在漏極串聯(lián)電阻或∏型阻性衰減器,通常接在低噪聲放大器末級(jí)或末前級(jí)輸出口。而目前提高電路穩(wěn)定性常用的是引入負(fù)反饋。

1.2 功率增益以及增益平坦度

放大電路的增益是放大電路最重要性能指標(biāo),也是設(shè)計(jì)放大電路的一個(gè)基本參數(shù)。因此在放大器的設(shè)計(jì)中增益指標(biāo)的完成很是重要,功率增益主要有3種描述方式:可用功率增益GA,工作功率增益GP,轉(zhuǎn)換功率增益GT。

增益平坦度對(duì)于低噪聲放大電路來(lái)說(shuō),就是全頻帶范圍內(nèi)增益變化要平緩,不允許增益變化陡變。

1.3 噪聲系數(shù)

噪聲系數(shù)是LNA的另一重要指標(biāo),如果接收系統(tǒng)噪聲系數(shù)過(guò)大,信號(hào)會(huì)被噪聲埋沒(méi),致使接收系統(tǒng)的靈敏度減小。

1.4 駐波比

低噪聲放大器通常用輸入輸出駐波比來(lái)表示輸入輸出信號(hào)的反射損耗,輸入輸出駐波比過(guò)大時(shí)不僅會(huì)損壞與低噪聲放大器級(jí)聯(lián)的器件還會(huì)使系統(tǒng)的增益起伏和群遲延變壞,因此低噪聲放大器的輸入輸出駐波比應(yīng)該滿足一定要求,在一般系統(tǒng)中功率放大器的輸入輸出駐波比要小于2。

2 低噪聲放大器的電路設(shè)計(jì)步驟

2.1 晶體管器件的選擇和級(jí)數(shù)的確定

隨著器件工藝技術(shù)的發(fā)展,人們開發(fā)了許多新型的半導(dǎo)體器件。除砷化鉀場(chǎng)效應(yīng)晶體管(GaAs FET)外,其佼佼者有高電子遷移率晶體管(HEMT)和異質(zhì)結(jié)雙極晶體管(HBT)。根據(jù)有關(guān)資料對(duì)3種主要器件的介紹和比較,我們知道HEMT可以提高跨導(dǎo)和電流密度,而且它能減小電路對(duì)工藝的敏感性,用HEMT制作的多級(jí)低噪聲放大器已廣泛用于衛(wèi)星接收系統(tǒng)、電子系統(tǒng)及雷達(dá)系統(tǒng)。所以本設(shè)計(jì)選用HP公司的ATF-35176來(lái)進(jìn)行低噪聲放大器的設(shè)計(jì)。該器件是一種低噪聲砷化鎵PHEMT器件,適用于工作在2~18 GHz的低噪聲放大器,滿足設(shè)計(jì)要求。

另外考慮放大器的增益指標(biāo),由于一般的單管增益為9~12 dB,本設(shè)計(jì)的低噪聲放大器目標(biāo)需達(dá)到30 dB的增益,因此采用了三級(jí)級(jí)聯(lián)放大電路。

2.2 晶體管直流分析

靜態(tài)工作點(diǎn)的選擇直接關(guān)系到放大電路的各種性能,所以結(jié)合ATF35176的使用手冊(cè)上的數(shù)據(jù)對(duì)該晶體管的傳輸特性進(jìn)行分析,選擇合適的靜態(tài)工作點(diǎn)。

2.3 偏置電路設(shè)計(jì)

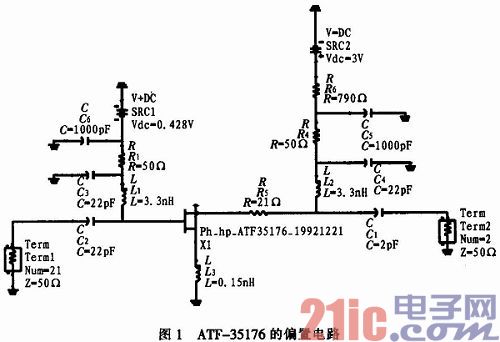

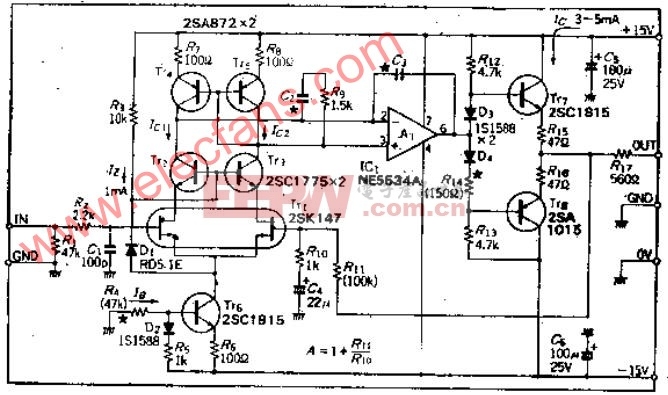

直流偏置電路根據(jù)外加電源可以分為2種:一種是雙電源供電,另一種是單電源供電。單電源供電一般用于微波較低頻段,單電源供電電路結(jié)構(gòu)簡(jiǎn)單,但是對(duì)于噪聲有一定影響。雙電源供電一般用于比較高的微波頻段,因?yàn)樗梢栽诟哳l段提供較好的噪聲特性。本論文采用的就是正負(fù)雙電源供電,有利于低噪聲設(shè)計(jì),偏置電路如圖1所示。

2.4 穩(wěn)定性分析

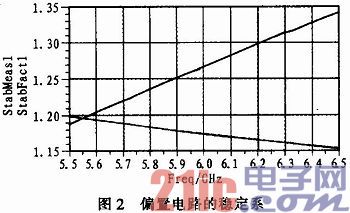

由于對(duì)偏置電路進(jìn)行仿真得到穩(wěn)定系數(shù)結(jié)果如圖2所示,可以從圖中看出在整個(gè)工作頻段,放大器處于絕對(duì)穩(wěn)定狀態(tài),所以無(wú)需進(jìn)行穩(wěn)定性設(shè)計(jì)。

2.5 輸入匹配電路設(shè)計(jì)

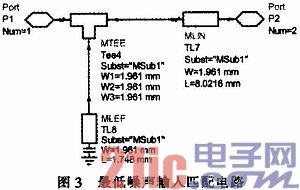

由于本設(shè)計(jì)采用多級(jí)放大,而第一級(jí)放大器的噪聲系數(shù)對(duì)整個(gè)低噪聲放大器電路的影響起這決定性作用,所以第一級(jí)放大器按照最小噪聲系數(shù)對(duì)輸入端進(jìn)行匹配,采用smith圓圖工具進(jìn)行匹配,得到的輸入匹配電路如圖3所示。

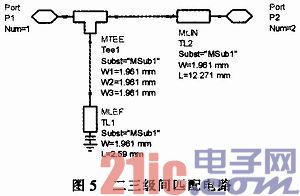

2.6 級(jí)間匹配

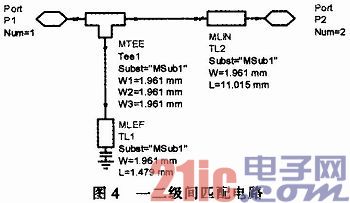

級(jí)間匹配電路的基本任務(wù)是使后級(jí)微波管輸入阻抗與前級(jí)微波管輸出阻抗匹配,以獲得較大增益。因?yàn)榈谝患?jí)的設(shè)計(jì)是按最低噪聲設(shè)計(jì)的,并沒(méi)有使增益達(dá)到最大,所以第二級(jí)的噪聲對(duì)整體的影響也是十分明顯的,因此第一二級(jí)間的匹配也要偏重噪聲系數(shù),匹配電路如圖4所示。而二三級(jí)間的匹配電路按照最大增益匹配設(shè)計(jì),匹配電路如圖5所示。

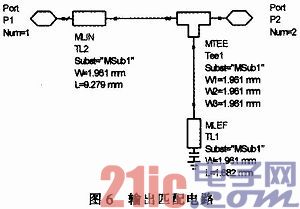

2.7 輸出匹配電路設(shè)計(jì)

輸出匹配電路的設(shè)計(jì)主要考慮增益和駐波比,基本任務(wù)是把微波管復(fù)數(shù)輸出阻抗匹配到負(fù)載實(shí)數(shù)阻抗,從而提高增益和輸出駐波比,匹配電路如圖6所示。

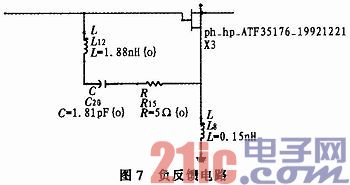

2.8 負(fù)反饋電路

為了適當(dāng)改善放大器增益平坦度,在晶體管柵源之間采用負(fù)反饋網(wǎng)絡(luò)所示,具體電路如圖7所示。

實(shí)際上負(fù)反饋網(wǎng)絡(luò)除了拓寬頻帶、改善增益平坦度外,還參與了匹配并改善輸入輸出駐波,其優(yōu)點(diǎn)是便于充分發(fā)揮PHEMT電路的低噪聲和高增益特性。

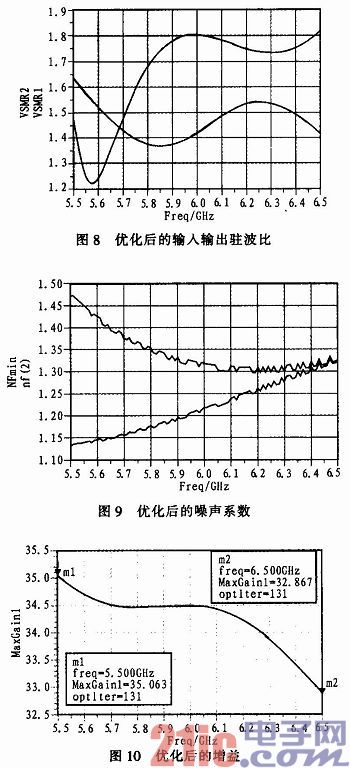

2.9 整體電路仿真優(yōu)化

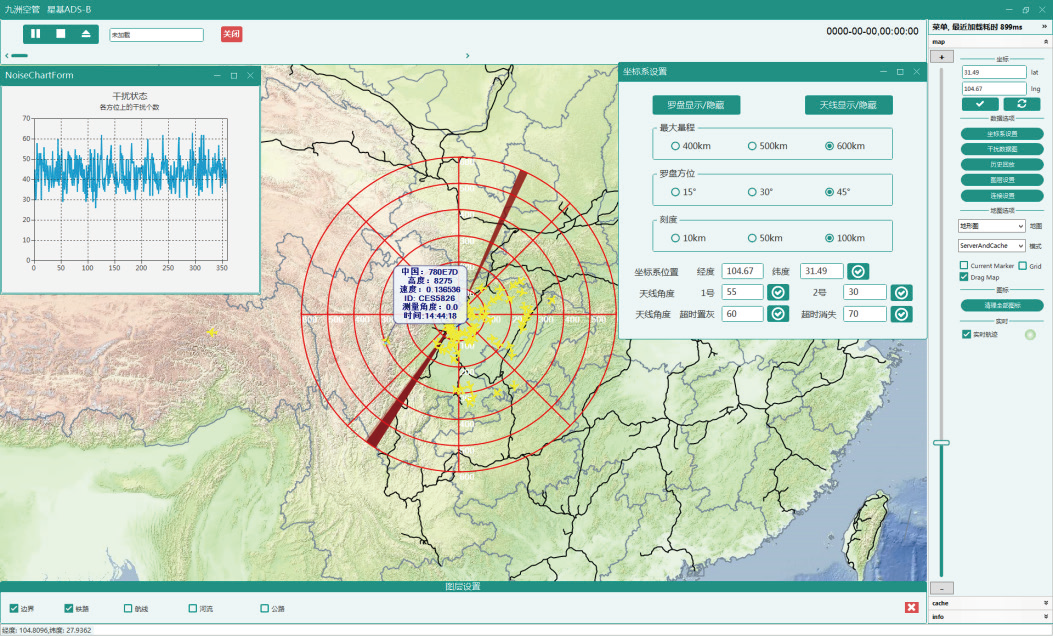

采用ADS中的優(yōu)化功能,對(duì)原理圖中微帶線的長(zhǎng)度、電容與電感值進(jìn)行優(yōu)化,最后得到滿足要求的低噪聲放大器。其仿真所得的駐波比、噪聲系數(shù)以及增益分別如圖8、圖9、圖10所示。

通過(guò)ADS仿真,噪聲放大器工作在5.5~6.5 GHz波段,增益大于32.8 dB,噪聲系數(shù)小于1.5 dB,駐波比小于2,滿足設(shè)計(jì)需求。

3 結(jié)束語(yǔ)

文中主要采用三級(jí)放大,低噪聲放大器選用ATF-35176晶體管,通過(guò)仿真分析,完成了偏置電路以及輸入、級(jí)間和輸出的匹配電路設(shè)計(jì),并采用ADS軟件進(jìn)行全部電路的優(yōu)化仿真,仿真結(jié)果表明,低噪聲放大器工作在5.5~6.5 GHz波段,增益大于32.8 dB,噪聲系數(shù)小于1.5 dB,駐波比小于2,達(dá)到了設(shè)計(jì)指標(biāo)的要求。本設(shè)計(jì)還有進(jìn)一步改善的可能,接下來(lái)將繼續(xù)采用一些其他的設(shè)計(jì)結(jié)構(gòu)來(lái)改善此設(shè)計(jì)。

評(píng)論