采用FPGA實現(xiàn)四階IIR數(shù)字濾波電路設計

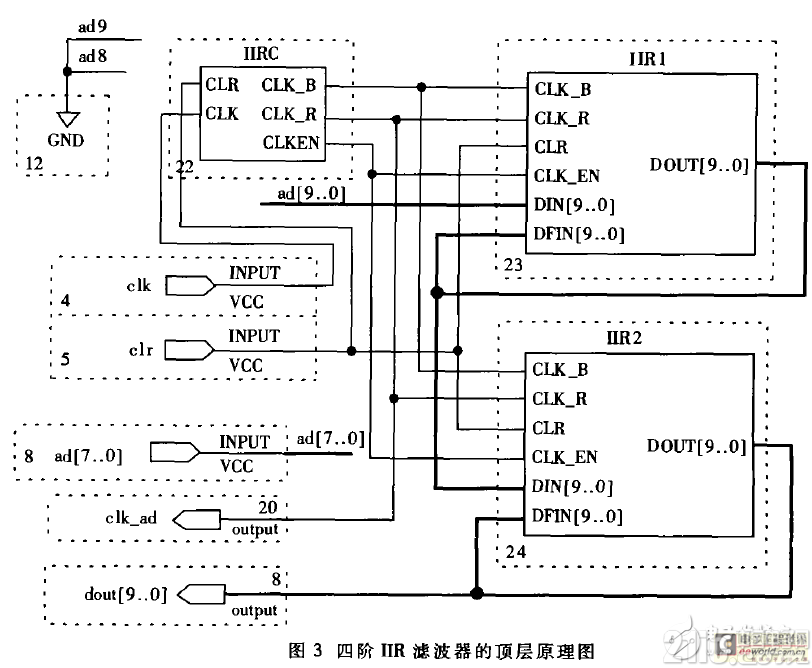

采用FPGA實現(xiàn)四階IIR數(shù)字濾波器,通過兩個二階節(jié)級聯(lián)構成數(shù)字橢圓低通濾波器。通帶內波紋小于0.1dB,阻帶衰減大于32dB。常用的數(shù)字濾波器有FIR數(shù)字濾波器和IIR數(shù)字濾波器。FIR數(shù)字濾波器具有精確的線性相位特性, 在信號處理方面應用極為廣泛,而且可以采用事先設計調試好的FIR數(shù)字濾波器IP Core來完成設計。另外,對于相同的設計指標,F(xiàn)IR濾波器所要求的階數(shù)比IIR濾波器高5~10倍,成本較高,而且信號的延遲也較大。IIR濾波器所要求的階數(shù)不僅比FIR濾波器低,而且可以利用模擬濾波器的設計成果,設計工作量相對較小,采用FPGA實現(xiàn)的IIR濾波器同樣具有多種優(yōu)越性。

本文引用地址:http://www.104case.com/article/201610/307924.htm

數(shù)字濾波器實際上是一個采用有限精度算法實現(xiàn)的線性非時變離散系統(tǒng),它的設計步驟為:首先根據(jù)實際需要確定其性能指標,再求得系統(tǒng)函數(shù),最后采用有限精度算法實現(xiàn)。根據(jù)需要,本系統(tǒng)的設計指標為:模擬信號采樣頻率為2MHz,每周期最少采樣20點,即模擬信號的通帶邊緣頻率為fp=100kHz,阻帶邊緣頻率 =1MHz,通帶波動 不大于0.1dB (通帶誤差不大于5%),阻帶衰減A s不小于32dB。系統(tǒng)函數(shù)的計算采用Matlab軟件比較方便。

本文采用一個折中的方法實現(xiàn),即乘加單元(MAC)的乘法器采用陣列乘法器,而不使用串行乘法器,以提高運算速度。需要注意的是,MAX+plus II的LPM庫中乘法運算為無符號數(shù)的陣列乘法,所以使用時需要先將兩個補碼乘數(shù)轉換為無符號數(shù)相乘后,再將乘積轉換為補碼乘積輸出。每個二階節(jié)完成一次運算共需要6個時鐘周期, 而且需采用各自獨立的MAC實現(xiàn)兩級流水線結構,即每個數(shù)據(jù)經過兩個二階節(jié)輸出只需要6個時鐘周期。

評論