一次性可編程時鐘產生器OmniClock可提供最高設計靈活性和豐富功能

時鐘是電子系統中的關鍵元素,其性能對整個系統的穩定運行有著至關重要的作用。OmniClock,是安森美半導體推出的可高度定制的一次性可編程時鐘產生器系列,其靈活性冠于市場上任何可編程時鐘器件,可用于可穿戴、智能手機、攝相機、電子書、便攜式電子和物聯網等寬廣的應用,具有小尺寸、低功耗、低成本、改善的串擾/抖動性能等優勢。

本文引用地址:http://www.104case.com/article/201610/307813.htmOmniClock系列特性及設計優勢

OmniClock系列支持從8 kHz到200 MHz的任意輸出頻率,有三個單端時鐘輸出(LVCMOS/LVTTL),兩者可以組合成一個差分輸出(LVPECL、LVDS、HCSL / CML),令設計人員可替代多個晶體和/或振蕩器,降低整體系統成本。如NB3H63143G,可同時提供一個50 MHz、125 MHz和48 MHz時鐘分別到CPU核、物理層和CPU核以實現最佳主時鐘(BMC)算法,或同時提供一個味50 MHz和一個差分156.25 MHz(LVPECL)時鐘到控制面板的復雜可編程邏輯器件(CPLD)和以太網;又如NB3V60113G,可提供一個25 MHz± 0.125 %的時鐘到固態硬盤(SSD)模塊的CPU核,或提供一個27 MHz± 0.5%的時鐘到CMOS傳感器的MCLK主時鐘。

OE:輸出使能

VDDO:輸出電壓

表1. 安森美半導體的全系列OmniClock產生器

1.提供可高度定制的靈活性

OmniClock是具有編程軟件Clock Cruiser的全定制器件,可配置的參數包括輸出頻率、輸出類型、驅動電流、輸出引腳、內部負載電容、電源電壓、輸出電壓、參考輸入、控制引腳、鎖相環(PLL)旁路特性及擴頻配置等等,在系統測試過程中,在器件配置間可快速切換, 架構最佳的性能方案。此外,設計人員可存儲達4個獨立的配置到一次性可編程內存(OTPM),便于在輸出要求相似時可直接啟用配置,縮減開發時間和減低庫存。

2.提升系統可靠性

利用晶體來產生時鐘信號,可能會出現一系列問題,如線路板布板和布線、溫度和電壓、啟動時間長、需要額外元件如負載電容等。通過用OmniClock產生器替代晶體及機械式元件,可減少系統各種故障,提升系統可靠性。

3.降低系統EMI (電磁干擾) 峰值

電路板上元件之間的布線可能產生潛在的噪聲和EMI, OmniClock內部PLL提供完全可編程的擴頻頻率調制,通過各種不同的擴頻配置可解決系統EMI峰值干擾問題。擴頻方面,設計人員可選擇擴頻類型如不擴頻、中心擴頻或下行擴頻,偏離百分比如中心擴頻以0.125%步幅的±0.125% 至±3%、或下行擴頻以0.25%步幅的-0.25%至-4%,頻率調制可選30KHz 至130KHz之間的任意值。擴頻調制基于PLL的輸出,工作于PLL旁路模式的將不受影響。這需要在輸入時鐘頻率和所需的擴頻配置間進行權衡。

4.節省空間,降低成本

由于OmniClock省去晶體及晶體振蕩器、負載電容,節省占板空間,從而簡化物料單,降低復雜度和系統成本,加之采用非常小的QFN-16和DFN-8封裝,體積非常小,滿足可用空間極小的應用需求。

5.低功耗

低功耗是OmniClock系列的一個關鍵優勢,可延長終端產品如便攜式消費設備的電池使用時間。

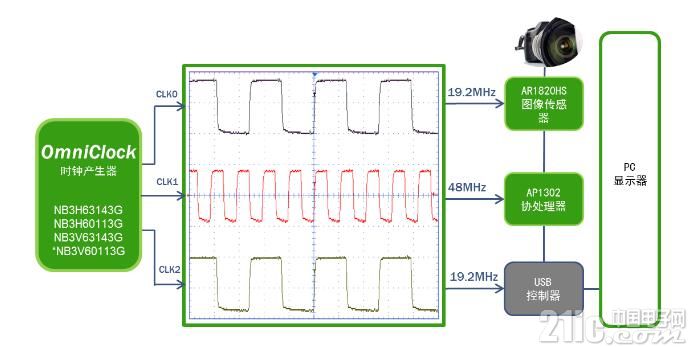

OmniClock用于USB視頻類攝像機改善串擾/抖動

USB視頻類攝像機通常需要多個參考時鐘用于圖像傳感器、圖像協處理器及USB控制器模塊運行于不同頻率,利用時鐘產生及緩沖器進行系統設計,可改善串擾/抖動,提供更好的布局靈活性,并易于以具有優勢的成本進行系統升級。

單個OmniClock器件配置為支持USB視頻類攝像機所需的3個頻率:提供一個19.2 MHz時鐘到AR1820HS 1800萬像素圖像傳感器,一個48 MHz時鐘到AP1302圖像協處理器,和一個19.2 MHz時鐘到一個USB控制器,替代晶體和晶體振蕩器。可定制的頻譜配置令該系列器件適用于對EMI敏感的應用而不犧牲成像性能。其靈活性進一步支援制造進程,能通過編程軟件驗證動態口令(OTP)參數,而其小封裝設計降低電路板復雜度和成本。

圖1. OmniClock提供USB視頻類攝像機所需的3個頻率時鐘

由于在網絡攝像機系統設計中采用較長的扁平電纜,像素時鐘會產生EMI諧波峰值。OmniClock擴頻配置可解決應用敏感的EMI峰值問題,不降低成像性能,無需修改硬件。以NB3V60113G為例,如表2所示,對于配置分別為全分辨率、16M16fps、4k30fps、1080p120fps的圖像傳感器,晶體振蕩器幀速率分別為14.4 fps、15.8 fps、28.8 fps、115.2 fps,NB3V60113G采用0%至+/- 3%的百分比進行擴頻,幀速率仍然保持不變。

表2. OmniClock擴頻配置不降低成像性能

設計注意事項

為有好的時鐘信號完整性以盡量減小數據誤差,有必要減少信號反射。反射系數只有在源阻抗等于負載阻抗時為零。因而需要匹配阻抗以減少信號反射。可通過在輸出引腳附近增添一個串聯電阻來最大限度地減小阻抗差異。

為使器件不受到系統電源噪聲的影響,需貼裝一個0.1 uF和一個2.2 uF的去耦電容到線路板,且盡可能離VDD引腳近。到VDD引腳的線路板走線和接地通孔應當盡可能薄和短。所有VDD引腳都應當有去耦電容。

差分信號如LVDS具有共模噪聲抑制和低噪聲的固有優勢,支持快速開關速度,且功耗較其它差分信號標準低,扇出的LVDS緩沖可用作擴展以提供時鐘信號到多個LVDS接收器,驅動多個點對點鏈接到接收節點。

總結

OmniClock系列為當前市場上任何可編程的時鐘器件提供最多的功能和靈活性,該系列器件接受一系列晶體或參考時鐘輸入頻率以產生一路差分輸出(LVPECL, LVDS, HCSL, CML) 加一路單端,或以用戶定義的頻率達三路單端LVCMOS輸出,支持從8 KHz到200 MHz的任意輸出頻率,替代晶體和/或振蕩器,節省占板面積,降低整體系統成本,超越完全采用分立晶體的系統,改善串擾/抖動,增強系統可靠性,同時大大簡化電路板設計,并使客戶能滿足他們系統低功耗的要求,比晶體縮短交期,可定制的擴頻配置還可用于對EMI敏感的應用。

關注安森美半導體官方微信,了解更多創新的高能效方案

評論