基于FPGA的多路視頻收發系統的設計與實現

摘要:為了實現對多路視頻和數據信號的同步傳輸,提出了一種基于FPGA的視頻數據綜合傳輸系統設計方案,并完成系統的軟硬件設計。該系統的硬件部分主要由FPGA、CPLD芯片及光模塊等設備組成,軟件部分采用VHDL語言進行邏輯編程,能夠完成整個收發系統的全部功能。實際工程應用表明,該系統具有成本合理、操作簡便、性能穩定的特點,達到了設計要求。

本文引用地址:http://www.104case.com/article/201610/307180.htm隨著人們安全意識的不斷提高,對現代化視頻監控技術也有了進一步要求,先進的視頻、音頻、數據的綜合傳輸設備得到廣泛的應用,因此,對綜合業務傳輸性能的要求也越來越高。如何在控制成本的基礎上,開發性能穩定、信號完整的綜合傳輸系統,是廣大傳輸設備開發工程師需要思考的問題。目前,在成本有限的情況下,市面上所見的綜合業務傳輸設備大多有性能不太穩定、傳輸類型單一、容易亂碼、斷網等缺陷。比如,僅可收發視頻信號,沒有語音信號,或是數據信息有缺失、畫面抖動、時斷時續的現象。因此,做到視頻、數據、語音等多種信號的同步、穩定疊加,對于整個綜合業務傳輸設備在成本控制的情況下,產品還有很大的提升空間。

在壓縮工程應用成本的基礎上,對視頻、數據、語音等信號的安全、有效傳輸將是本文的研究重點。為了實現對綜合業務的準確傳輸,在做了詳盡的需求分析基礎上,提出并設計了一種基于FPGA的多路視頻收發系統(以下簡稱“收發系統”)的硬件及軟件設計方案。經多次測試及工程實際應用表明,該系統能很好地完成綜合業務的有效傳輸。

1 總體設計

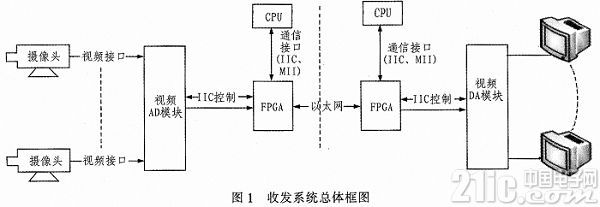

整個系統由兩端設備組成,兩端構成基本相同。習慣上,通常把視頻信號輸入的一端稱發送端,另一端則為接收端。發送端由攝像頭采集視頻信號,經AD轉換模塊,將模擬信號轉換為數字信號,經處理的數字視頻信號及其他數據信號在FPGA中進行編碼操作。其中,部分控制信號由外處理器給出指令。FPGA編碼處理后的信號,由光模塊經千兆以太網傳輸至接收端。在接收端,FPGA負責將千兆以太網傳輸過來的編碼數據進行解碼,部分指令仍由外處理器給出。處理好的數字視頻及其他數據經DA轉換模塊,將數字信號轉化為可識別的模擬信號,最終在顯示器上顯示出來。圖1給出“收發系統”總體框圖。

本著節約成本、降低功耗、有效與其他設備通用的原則,整個系統硬件采用基板和背板的形式,這也是目前電子、通信行業最為流行的一種設備安裝模式。設備核心為基板,負責完成高速數據復分接和光通道的建立,提供各種功能擴展接口,同時也提供最多4個視頻通道,剩余6路視頻信號則在視頻擴展板內完成通信。在背板的基礎上,插接各種功能的基板、擴展板。輔助通道擴展板通過背板與基板實現電源和信號連接,輔助通道擴展盤同時完成信號的中繼。將信號的傳輸分為各個單板來實現。此種結構,簡潔、大方、操作便利、便于糾錯。

2 系統硬件設計

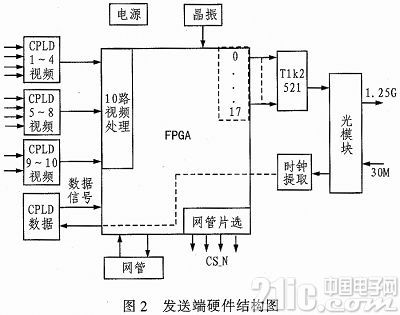

由于收發兩端的結構基本一致,這里僅發送端為例,概述系統核心板的硬件設計。發送端主要由基板、視頻擴展板、輔助通道擴展板1、輔助通道擴展板2等部分組成。其中以基板為核心,發送端硬件由FPGA主芯片、CPLD芯片、光模塊及其他一些外圍電路組成。FPGA主芯片負責處理十路視頻信號復分接及片選信號的復用,網管送信號入FPGA后,由3—8譯碼器翻譯出5種情況,分別送至4塊CPLD芯片和本身的FPGA,通過填報不同的網管信息,上報各個芯片的運轉情況。最終,由千兆收發器Tlk2521串行編碼,經1.25 G光模塊發送至接收端。

時鐘方面。晶振選用67.5 M,以67.5 M作為基本速率。Tlk2521并行處理的速率為67.5 M.正向光傳輸信號的速率為1.25 G。發射端的基本時鐘用當地時鐘,接收端用還回時鐘。收端送來的反向數據,由時鐘提取電路提取出時鐘和數據之后,送入FPGA進行同步處理。其結構圖如圖2所示。同步處理過程,將在FPGA的邏輯設計中進行詳細描述。

視頻信號采用8 bit量化方式,以13.5 M進行采樣。通過四路、四路、二路復接的形式送入FPGA中,再通過FPGA整合成10路16 bit的形式,由Tlk2521處理后送到光模塊中。同時,數據、音頻、網管等輔助業務的數據則由單獨的一個CPLD進行整合,通過一條線送入FPGA中,與視頻信號一起形成17 bit的數據進行傳輸,同步字由20位構成,利用其中1 bit進行傳輸。TLK2521有18 bit并行數據線,其中每根數據線占67.5M的帶寬,具體使用分配如下:0~7、8~15 bit傳視頻數據,第16 bit傳輔助業務數據,第17 bit傳輸同步字。高速信號采用16 bit并行擾碼,并行擾碼跟幀同步保持同步,使用20個擾碼字。

3 系統軟件設計

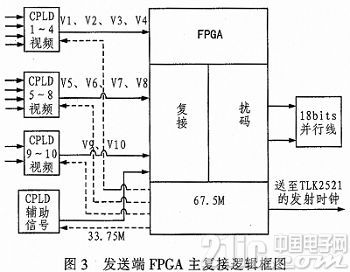

該收發系統FPGA芯片模塊編寫所使用的軟件為ISE,采用VHDL語言編程。VHDL是當前FPGA芯片編程常用的描述語言,其功能強大、設計靈活、支持廣泛、易于修改,具有強大的系統硬件描述能力、很強的移植能力、易于共享和復用。1~4路視頻信號經CPLD匯總接入基板,5~8路視頻信號經CPLD匯總,與9~10路視頻信號以及輔助信號一起經過復接,接入FPGA中,最后將所有信號經擾碼以18 bits并行數據線給出FPGA芯片。FPGA提供67.5 M采樣始終給千兆位串行收發器TLK2521。圖3給出發送端FPGA芯片復分接框圖。

在基板視頻復接中,通過FPGA送來的復接指示信號進行視頻復接,由CPLD本身產生的一個計數器對時鐘進行計數,5個時鐘周期為一個計數周期,為4路視頻開辟5個位置,把4路視頻依次復接,第5位置空出不填充數據,有效地錯開位置,從而實現非緩存的數據傳輸。在擴展板視頻復接中,復接的方式和基板視頻復接原理一樣,不同之處在于,復接的位置不一樣,擴展板的CPLD1在復接視頻時空出的第1個位置;CPLD2在復接時,由于只有2路視頻需要復接,所以第2、3、4位置空出。

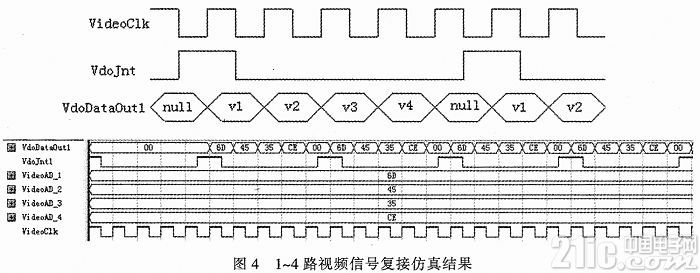

圖4以1~4路視頻信號復接為例,給出時鐘關系仿真圖。其中Vclk為67.5 M的時鐘信號;VdoJnt為視頻通道指示信號,一個時鐘周期寬度的脈沖信號,在67.5 M時鐘頻率下,每5個周期送出一個脈沖,VideoClk和VdoJnt都由FPGA送往CPLD;VdoDataOut1為4路視頻數據復接后的信號,此處按8 bits量化來定義;當復接指示VdoJnt為高電平,且在時鐘VideoClk的上升沿時,對視頻進行采樣復接,最后復接成VdoDataOut1信號送出。

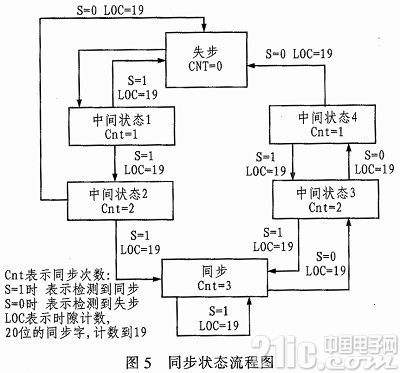

眾所周知,在FPGA邏輯設計中,最重要的是時鐘同步問題的解決。圖5給出FPGA同步狀態流程圖,其中,Cnt表示同步次數,S=1表示檢測到同步,S=0表示同步丟失,LOC對時隙計數,一共有20位同步,從0計數到19依照流程圖編寫同步判定程序,可完好地實現信號同步。

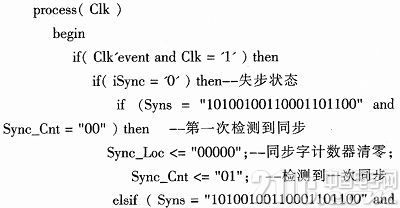

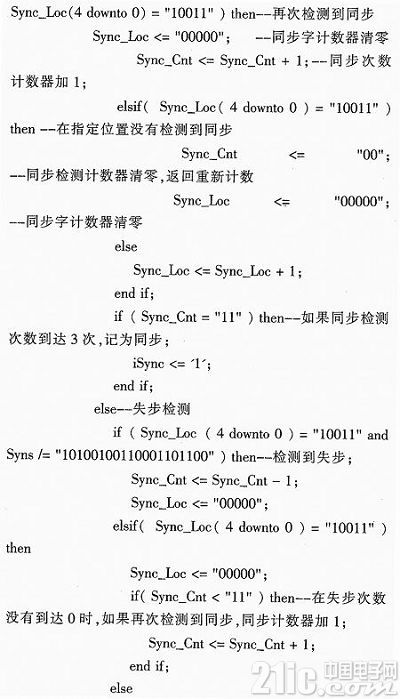

下面給出同步檢測模塊的部分程序,用來做同步和失步的檢測。

4 研發過程中出現的問題、解決辦法及效果

1)無視頻。FPGA的程序下載之后,視頻丟失,檢測AD和DA的輸入時鐘,發現DA時鐘輸入異常。原因是配置管腳錯誤,按著電路原理圖上說明的把DA管腳全部配置反了,后來修改過來之后視頻正常。

2)視頻位置錯亂。收端按照發端復接視頻的順序分接視頻,發現視頻順序錯位,1234分別成了2341,原因:傳輸延遲造成了視頻位置錯位,修改接收端CPLD程序,調整分接位置之后,視頻正常。

3)視頻出現花屏。分接之后的視頻有“花屏”現象出現,原因:時鐘沿采樣不準確。通過調整時鐘沿解決,把送入CPLD的時鐘取反,“花屏”現象消失。

4)視頻擴展板視頻指示燈異常。視頻擴展板指示燈異常,處于常亮狀態。原因:視頻指示燈短路。用萬用表查找時,發現在鉭電容的下方,多出了的焊錫把鉭電容下方的視頻指示燈的過孔堵住了,使得視頻線路短路,卸掉鉭電容后小心焊接,問題解決。

5)插拔光纖時同步丟失,并死機。在測試網管的時候,進行插拔纖測試時,一旦拔掉光纖,再接上會造成同步丟失并死機,需要重新燒寫程序方能解決。調整時序約束,把晶振時鐘的時序約束調整到100 M,問題解決。

6)開關電數據誤碼。在進行開關電測試時,發現數據誤碼,且收光指示燈閃爍異常。參閱FPGA時序約束文章發現,時序約束不宜過高,把原來LockID的時序設置為100 M改為80 M之后,問題解決。

5 結論

該“收發系統”是在充分的理論分析與市場需求基礎上做出的系統設計,經過詳盡的測試轉化為實際產品,該產品有效地降低了成本、提高了系統集成度,在一根光纖上實現了多種業務的綜合傳輸,已應用于某安防系統,實際工程應用表明該系統具有收發信號準確、穩定性高、人機界面友好、易于操作、成本合理等特點,達到了設計要求。解決了實際工程應用中,低成本產品性能相對較差的缺陷,工程應用反應良好。

評論