基于FPGA的多路數(shù)字信號(hào)復(fù)接系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

摘要 數(shù)字復(fù)分接技術(shù)是數(shù)字通信網(wǎng)中的一項(xiàng)重要技術(shù),能將若干路低速信號(hào)合并為一路高速信號(hào),以提高帶寬利用率和數(shù)據(jù)傳輸效率。文中在介紹數(shù)字復(fù)接系統(tǒng)的基礎(chǔ)上,采用VHDL對(duì)數(shù)字復(fù)分接系統(tǒng)進(jìn)行建模設(shè)計(jì)和實(shí)現(xiàn)。并利用乒乓操作和先進(jìn)先出存儲(chǔ)器(FIFO)對(duì)復(fù)接器進(jìn)行設(shè)計(jì),利用幀同步器對(duì)數(shù)據(jù)進(jìn)行分接。以QuartusII8.0為仿真軟件,對(duì)設(shè)計(jì)進(jìn)行仿真驗(yàn)證,仿真結(jié)果表明,設(shè)計(jì)實(shí)現(xiàn)了復(fù)接系統(tǒng),便于修改電路結(jié)構(gòu),增強(qiáng)了設(shè)計(jì)的靈活性,且節(jié)約了系統(tǒng)資源。

本文引用地址:http://www.104case.com/article/201610/306478.htm數(shù)字通信系統(tǒng)中,為了提高信道的利用率,使多路信號(hào)在同一條信道上傳輸時(shí)互相不產(chǎn)生相干的方式稱為多路復(fù)用。在時(shí)分復(fù)用中,將時(shí)間劃分為若干時(shí)隙,各路信號(hào)在時(shí)間上占用各自的時(shí)隙,即多路信號(hào)在不同時(shí)間內(nèi)被傳送,各路信號(hào)在時(shí)域中互不重疊。數(shù)字復(fù)接終端是將若干低速率碼流變換成一路高速率碼流的設(shè)備。應(yīng)用可編程邏輯門陣列(FPGA)芯片實(shí)現(xiàn)復(fù)接系統(tǒng)便于修改電路結(jié)構(gòu),增強(qiáng)了設(shè)計(jì)的靈活性,并節(jié)約了系統(tǒng)資源。

1 多路復(fù)接系統(tǒng)設(shè)計(jì)要求

(1)實(shí)現(xiàn)兩路數(shù)據(jù)的同步復(fù)接。(2)支路速率為32 kbit·s-1。(3)按位復(fù)接。(4)幀同步碼字為10 bit:“1 0 1 1 0 1 0 01 1”。(5)幀長128 bit。

2 數(shù)字復(fù)接系統(tǒng)基本原理

數(shù)字復(fù)接終端的作用是將低速數(shù)據(jù)碼流變換成高速數(shù)據(jù)碼流的設(shè)備。將兩個(gè)或兩個(gè)以上的支路數(shù)字信號(hào)按時(shí)分復(fù)用方式合并成單一的合路數(shù)字信號(hào)的過程稱為數(shù)字復(fù)接;完成數(shù)字復(fù)接功能的設(shè)備稱為數(shù)字復(fù)接器;在接收端將一路復(fù)合數(shù)字信號(hào)分離成各支路信號(hào)的過程稱為數(shù)字分接。數(shù)字復(fù)接器、數(shù)字分接器和傳輸傳道共同構(gòu)成了數(shù)字復(fù)接系統(tǒng)。

2.2 按位復(fù)接

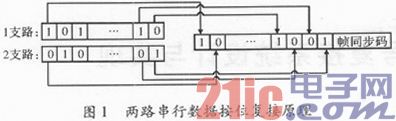

復(fù)接的方式有:按位、按字和按幀復(fù)接等方式。本文采用按位復(fù)接的方法,方法是每次僅依次復(fù)接每一個(gè)支路的一位碼,又稱比特復(fù)接。復(fù)接后的碼序列中第一個(gè)時(shí)隙中的第一位表示第一路的第一位碼;第二位表示第二路的第一位碼;依此類推,則第n位表示第n路的第一位碼。2路串行數(shù)據(jù)按位復(fù)接原理框圖如圖1所示。

3 數(shù)字復(fù)接系統(tǒng)的建模與仿真

3.1 復(fù)接器總體設(shè)計(jì)方案

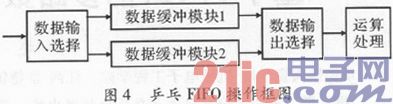

復(fù)接器的設(shè)計(jì)方案如下:首先對(duì)兩支路串行數(shù)據(jù)數(shù)字信號(hào)進(jìn)行按位復(fù)接合成一路信號(hào);用FIFO定義2個(gè)128 bit幀格式,幀同步碼為10 bit“1011010011”,采用乒乓操作對(duì)合路數(shù)據(jù)每118位依次存儲(chǔ)到FIFO中,即將合路數(shù)每118位插入一個(gè)幀同步碼,形成128位的幀。乒乓操作是輸入合路數(shù)據(jù)流通過輸入數(shù)據(jù)選擇單元等時(shí)地將數(shù)據(jù)流分配到兩個(gè)FIFO數(shù)據(jù)緩沖區(qū)。當(dāng)FIFO緩沖區(qū)1寫入數(shù)據(jù)操作時(shí),從FIFO緩沖區(qū)2中讀取數(shù)據(jù)操作;當(dāng)FIFO緩沖區(qū)1讀數(shù)據(jù)操作時(shí),F(xiàn)IFO緩沖區(qū)2中進(jìn)行寫操作;如此循環(huán),可實(shí)現(xiàn)2路數(shù)據(jù)復(fù)接,具體如圖2所示。

3.2 復(fù)接器關(guān)鍵模塊設(shè)計(jì)

(1)合路模塊。合路模塊功能是將兩路串行數(shù)據(jù)按位復(fù)接成一路數(shù)據(jù),合路模塊輸出的是未接入幀同步碼的數(shù)據(jù),對(duì)于各支路數(shù)據(jù)輸入需使用clksel時(shí)鐘作為控制。合路輸出為y信號(hào),D0、D1是兩路串行數(shù)據(jù),clksel是兩支路控制輸出信號(hào)。從仿真圖3中可看出,其能將D0和D1合成一路信號(hào)y輸出,仿真結(jié)果正確。

(2)乒乓操作FIFO模塊。乒乓操作FIFO模塊的功能是對(duì)合路數(shù)據(jù)加入幀同步碼。乒乓操作FIFO框圖如圖4所示。乒乓操作處理流程如下:輸入數(shù)據(jù)流通過輸入數(shù)據(jù)選擇單元將數(shù)據(jù)流分配到兩個(gè)數(shù)據(jù)緩沖區(qū)。在第1個(gè)緩沖周期中,將輸入的數(shù)據(jù)流緩存到數(shù)據(jù)緩沖模塊1;在第2個(gè)緩沖周期中,通過輸入數(shù)據(jù)選擇單元的切換,將輸入的數(shù)據(jù)流緩存到數(shù)據(jù)緩沖模塊2。同時(shí),將數(shù)據(jù)緩沖模塊1緩存的第1個(gè)周期的數(shù)據(jù)通過輸出數(shù)據(jù)選擇單元的選擇,送到運(yùn)算處理單元進(jìn)行處理;在第3個(gè)緩沖周期,再次切換數(shù)據(jù)的進(jìn)入與輸出緩沖模塊。

空滿信號(hào)的產(chǎn)生是設(shè)計(jì)FIFO的關(guān)鍵之一,本文通過異步的比較讀寫指針ptr以及讀寫指針的MSB進(jìn)行判斷,然后產(chǎn)生兩個(gè)異步的空滿標(biāo)志信號(hào)送入讀寫模塊進(jìn)行同步,最后向外界輸出兩個(gè)同步的空滿信號(hào)。圖5的方框內(nèi)可看出空判斷信號(hào)atmpty和滿判斷信號(hào)afull是取反的關(guān)系。當(dāng)一個(gè)RAM數(shù)據(jù)讀完時(shí),另一個(gè)RAM寫滿。

圖6中input,是M序列偽隨機(jī)碼,“10011101”作為測試信號(hào)。可認(rèn)為M序列偽隨機(jī)碼是由兩支路信號(hào)合路而得到的信號(hào)。從仿真波形可看出,空滿判斷信號(hào)rmsb和wrsb1互為取反關(guān)系,滿足要求。rptr是讀地址信號(hào)從FIFO的首地址開始讀取數(shù)據(jù)的。wptr寫地址信號(hào)是從FIFO的第10個(gè)存儲(chǔ)單元開始寫入數(shù)據(jù)的,這是因?yàn)镕IFO的前10個(gè)存儲(chǔ)單元使用的是做幀同步碼“1011010011”。zongshu信號(hào)端是隨機(jī)碼加入幀同步碼后的輸出。

3.3 分接器關(guān)鍵模塊設(shè)計(jì)

圖7是分接器的原理框圖。定時(shí)發(fā)生器為幀同步系統(tǒng)提供幀定位標(biāo)志信號(hào);幀同步系統(tǒng)用來檢測所傳輸數(shù)據(jù)碼流中的幀同步碼;比特分接電路則用于將串行數(shù)據(jù)轉(zhuǎn)換為并行數(shù)據(jù)。

(1)幀同步碼檢測。幀同步碼檢測電路由10位移位寄存器組成,將幀同步碼設(shè)定為10位最佳碼“1011010011”,當(dāng)電路檢測到輸入碼流中有幀同步碼組時(shí),檢測電路將輸出“0”;否則將輸出‘1’。輸出結(jié)果將作為定時(shí)發(fā)生器的控制信號(hào)之一。仿真波形如圖8所示,方框內(nèi)表示搜索得到的幀頭。幀頭為“1011010011”。

(2)定時(shí)發(fā)生器。定時(shí)發(fā)生器可對(duì)時(shí)鐘clk進(jìn)行n分頻,分頻后的周期等于幀周期。定時(shí)發(fā)生器主要用以產(chǎn)生幀定位標(biāo)志信號(hào),仿真波形如圖9所示。從框中可看出幀定位標(biāo)志信號(hào)。

(3)分路電路。兩路數(shù)據(jù),可采用一路利用上升沿觸發(fā),另一路用下降沿觸發(fā)。進(jìn)而將數(shù)據(jù)存到D鎖存器后,再進(jìn)行輸出。這便可將一路數(shù)據(jù)變成兩路。

該分路模塊的輸入是二級(jí)緩存的輸出,如圖10所示。

3.4 復(fù)分接系統(tǒng)總體設(shè)計(jì)

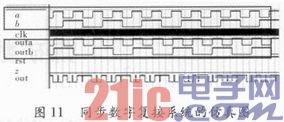

將所設(shè)計(jì)的復(fù)接器與分接器相連接,從仿真圖11中可看出,輸出的兩支路信號(hào)outa和outb的信號(hào)和復(fù)接前輸入的兩支路信號(hào)a和b的速率,與所包含的信息完全對(duì)應(yīng)。分別改變輸入信號(hào)a和b,最后分接出的信號(hào)同復(fù)接前的輸入信號(hào)一致,證明了設(shè)計(jì)的復(fù)分接系統(tǒng)的正確性和可靠性。

4 結(jié)束語

文中介紹了復(fù)分接系統(tǒng)的原理,并給出2路復(fù)分接系統(tǒng)建模方案。利用FIFO定義2個(gè)128 bit幀格式,10 bit幀同步碼,采用乒乓操作對(duì)合路數(shù)據(jù)每118位依次存儲(chǔ)到FIFO中,再將合路數(shù)每118位插入一個(gè)幀同步碼,形成128位的幀,即可實(shí)現(xiàn)兩路復(fù)接。同時(shí)對(duì)來自復(fù)接器的串行碼流進(jìn)行自動(dòng)幀識(shí)別定位分接,實(shí)現(xiàn)主碼流中兩個(gè)支路串行數(shù)據(jù)的同步復(fù)接。本系統(tǒng)中各模塊的仿真均在QuartusII 8.0中得到了驗(yàn)證。

評(píng)論