基于FPGA的水聲信號采集與存儲系統(tǒng)設(shè)計(jì)

摘要:為實(shí)現(xiàn)對水聲信號的多通道同步采集并存儲,提出了一種基于FPGA的多通道信號同步采集、高速大容量實(shí)時(shí)存儲的系統(tǒng)設(shè)計(jì)方案,并完成系統(tǒng)的軟硬件設(shè)計(jì)。該系統(tǒng)的硬件部分采用模塊化設(shè)計(jì),通過FPGA豐富的外圍接口實(shí)現(xiàn)模塊間的數(shù)據(jù)交互,軟件部分采用Verilog HDL硬件描述語言進(jìn)行編程,能夠靈活的實(shí)現(xiàn)信號的采集及存儲。實(shí)際應(yīng)用表明,該設(shè)計(jì)具有功耗低,可高速實(shí)時(shí)存儲,存儲容量大,通用性強(qiáng),易于擴(kuò)展升級等特點(diǎn)。

本文引用地址:http://www.104case.com/article/201610/306364.htm水聲信號采集存儲系統(tǒng)是海洋環(huán)境調(diào)查儀器的重要組成部分。開展水聲環(huán)境調(diào)查所使用的海洋儀器要求設(shè)備通道多、同步性好、采樣率高、數(shù)據(jù)存儲容量大。市場上常見的數(shù)據(jù)采集器多是采集某些固定種類的信號,動(dòng)態(tài)范圍比較小,通道數(shù)一般也比較少,有些還要求與主機(jī)進(jìn)行接口等,這些都限制了其在水聲信號采集中的應(yīng)用。為滿足需要,本文設(shè)計(jì)了適合于水聲數(shù)據(jù)采集存儲的較為通用的系統(tǒng),系統(tǒng)單板具有8個(gè)采集通道,多個(gè)單板級聯(lián)可實(shí)現(xiàn)多通道同步采集、USB高速存儲。

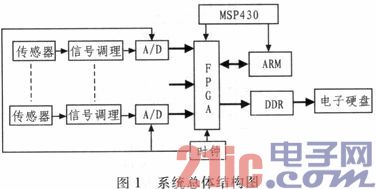

1 總體設(shè)計(jì)

該系統(tǒng)總體結(jié)構(gòu)如圖1所示,上級電路通過級聯(lián)接口發(fā)送采集指令,單片機(jī)初始化控制FPGA,控制FPGA首先判斷單板是否為級聯(lián)單板,再初始化相應(yīng)的FPGA。采集模塊的FPGA向需要同步采集的通道對應(yīng)的A/D芯片提供統(tǒng)一的時(shí)鐘,使得A/D同步的選擇相應(yīng)的通道進(jìn)行數(shù)據(jù)的同步采樣和轉(zhuǎn)換,其結(jié)果傳給負(fù)責(zé)緩存的FPGA,緩存在DDR對應(yīng)的存儲空間,然后由ARM控制存儲模塊的FPGA從DDR空間讀取數(shù)據(jù)進(jìn)行本地存儲。

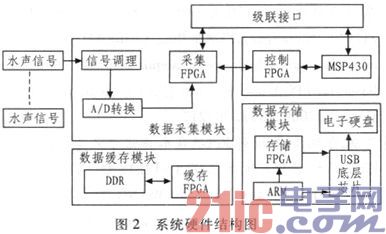

2 系統(tǒng)硬件設(shè)計(jì)

系統(tǒng)硬件主要由控制模塊、數(shù)據(jù)采集模塊、緩存模塊、存儲模塊幾部分組成,系統(tǒng)硬件結(jié)構(gòu)圖如圖2所示。單片機(jī)功耗低、接口豐富、可靠性高,被系統(tǒng)用做上電引導(dǎo)芯片;FPGA器件具有集成度高、內(nèi)部資源豐富、特別適合處理多路并行數(shù)據(jù)等明顯優(yōu)于普通微處理器的特點(diǎn),所以系統(tǒng)采用XILINX公司不同型號的FPGA作為不同模塊的主控芯片。針對系統(tǒng)設(shè)計(jì)中對采集存儲實(shí)時(shí)性和同步性的要求,存儲模塊采用FPGA與ARM相結(jié)合的設(shè)計(jì),采集主控制邏輯用ARM實(shí)現(xiàn),F(xiàn)PGA負(fù)責(zé)數(shù)據(jù)的高速傳輸和存儲。

控制模塊相當(dāng)于系統(tǒng)的值班電路,當(dāng)系統(tǒng)作為從板工作時(shí),只有控制模塊和數(shù)據(jù)采集模塊帶電,其他模塊關(guān)閉。由于FPGA內(nèi)核電壓只有1.2 V,在這種情況下系統(tǒng)工作電流不大于1 A,低功耗的設(shè)計(jì)保證系統(tǒng)可在無人值守的情況下長時(shí)間連續(xù)進(jìn)行采集存儲工作。系統(tǒng)需要多通道數(shù)據(jù)同時(shí)采集存儲時(shí),用戶通過配置主板的控制模塊參數(shù)設(shè)定8、16或32通道采集,主控FPGA通過級聯(lián)接口發(fā)送統(tǒng)一的采集時(shí)鐘到系統(tǒng)從板,從而實(shí)現(xiàn)系統(tǒng)多通道水聲信號的同步采集及存儲。另外,通過單片機(jī)接口也可以隨時(shí)監(jiān)控系統(tǒng)工作狀態(tài),系統(tǒng)具有修復(fù)功能,采集存儲過程中出現(xiàn)錯(cuò)誤時(shí),可根據(jù)用戶配置自動(dòng)進(jìn)行相應(yīng)的錯(cuò)誤處理。

數(shù)據(jù)采集模塊具有8路數(shù)據(jù)采集存儲通道,每通道采用TI公司的24位高精度模數(shù)轉(zhuǎn)換器ADS1258,A/D采用15.36 MHz的外部輸入時(shí)鐘。設(shè)計(jì)中數(shù)字電源、模擬電源、參考電壓單獨(dú)布線,保證8通道信號隔離度幾乎為零,降低了系統(tǒng)測量噪聲。模塊中FPGA并行控制多路數(shù)據(jù)轉(zhuǎn)換,包括轉(zhuǎn)換啟動(dòng)、轉(zhuǎn)換同步、轉(zhuǎn)換停止、轉(zhuǎn)換數(shù)據(jù)輸出等。

數(shù)據(jù)緩存模塊采用64M byte的DDR作為緩存,因?yàn)镈DR在一個(gè)時(shí)鐘周期內(nèi)進(jìn)行兩次數(shù)據(jù)傳輸操作,它能夠在時(shí)鐘的上升沿和下降沿各傳輸一次數(shù)據(jù),具有雙倍的數(shù)據(jù)傳輸量,DDR可以在與SDRAM相同的總線頻率下達(dá)到更高的數(shù)據(jù)傳輸率。緩存模塊中的FPGA對DDR的數(shù)據(jù)寫入和存儲

模塊中的FPGA對數(shù)據(jù)的讀取是通過兵乓傳輸結(jié)構(gòu)實(shí)現(xiàn)的。當(dāng)FPGA寫滿DDR上半?yún)^(qū)后,向存儲模塊申請中斷,存儲模塊響應(yīng)中斷后,讀出上半?yún)^(qū)數(shù)據(jù)到存儲模塊;同時(shí)FPGA向DDR的下半?yún)^(qū)寫數(shù)據(jù),寫滿下半?yún)^(qū)后也向存儲模塊發(fā)出中斷,通知存儲模塊讀出下半?yún)^(qū)數(shù)據(jù)。通過乒乓傳輸保證了系統(tǒng)數(shù)據(jù)采集和數(shù)據(jù)傳輸可連續(xù)進(jìn)行。

數(shù)據(jù)存儲模塊的作用是將多通道24 bit數(shù)據(jù)經(jīng)過緩存模塊,按采樣的時(shí)間順序,以低字節(jié)到高字節(jié)的次序,依次將其寫入電子硬盤。系統(tǒng)采用IPD的iPD-USB型300G電子硬盤作為存儲器。由于它沒有普通硬盤的旋轉(zhuǎn)介質(zhì),因而抗震性極佳,同時(shí)工作溫度很寬,可工作在-40~+85℃,再加上重量較硬盤輕很多,非常適用于水下聲信號采集存儲設(shè)備。根據(jù)系統(tǒng)要求,采用USB底層芯片配合存儲模塊實(shí)現(xiàn)大容量高速USB存儲,速度可達(dá)480Mbit/s,比全速USB存儲快了40倍。

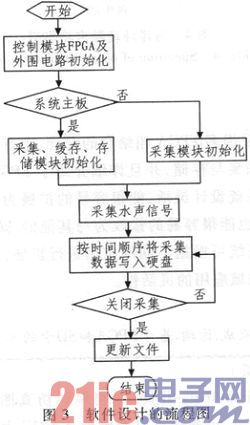

3 系統(tǒng)軟件設(shè)計(jì)

程序設(shè)計(jì)采用Verilog HDL硬件描述語言,軟件采用模塊化設(shè)計(jì),提高了程序的可移植性和可維護(hù)性。系統(tǒng)的軟件主要分為初始化模塊、水聲數(shù)據(jù)采集模塊、數(shù)據(jù)緩存模塊、數(shù)據(jù)存儲模塊、中斷服務(wù)程序模塊等構(gòu)成。初始化程序僅在系統(tǒng)復(fù)位及程序開始時(shí)執(zhí)行一次,完成各模塊主控芯片及外圍電路的初始化;數(shù)據(jù)采集模塊通過模擬量輸入端口采集水聲信號;數(shù)據(jù)緩存模塊負(fù)責(zé)將DDR中緩存的數(shù)據(jù)依次輸出給存儲模塊;數(shù)據(jù)存儲模塊每分鐘向電子硬盤中寫入一個(gè)文件。軟件設(shè)計(jì)的流程圖如圖3所示。

4 試驗(yàn)應(yīng)用

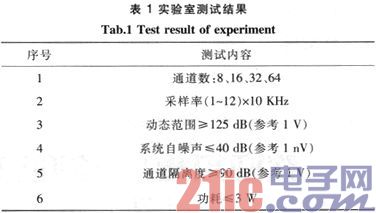

4.1 實(shí)驗(yàn)室測試結(jié)果

系統(tǒng)的性能測試是保證系統(tǒng)穩(wěn)定,可靠工作的重要手段。在實(shí)驗(yàn)室測試過程中,主要對系統(tǒng)的整體性能進(jìn)行考察,其中包括:多通道采集同步誤差、數(shù)據(jù)吞吐量、系統(tǒng)功耗、自噪聲等。測試結(jié)果如表1所示。

4. 2 海上試驗(yàn)結(jié)果

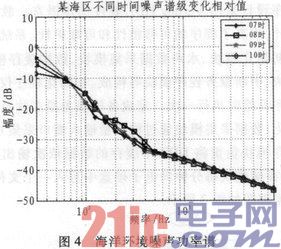

本系統(tǒng)應(yīng)用的海洋環(huán)境噪聲測量潛標(biāo)在中國某海域進(jìn)行了海上實(shí)驗(yàn),系統(tǒng)連續(xù)工作3個(gè)月,性能穩(wěn)定可靠,并獲取了大量完整有效的海洋環(huán)境噪聲數(shù)據(jù)。測量的海洋環(huán)境噪聲功率譜符合海洋環(huán)境噪聲的自然分布規(guī)律。實(shí)測海洋環(huán)境噪聲功率譜如圖4所示。

5 結(jié)論

本系統(tǒng)采用多FPGA相結(jié)合的設(shè)計(jì),很好的完成了高速多通道數(shù)據(jù)采集與存儲,并且詳細(xì)介紹了FPGA各模塊的設(shè)計(jì)方法。本系統(tǒng)設(shè)計(jì)靈活,能很容易的擴(kuò)展為多通道數(shù)據(jù)采集存儲系統(tǒng),也能很容易的修改為與其他的A/D轉(zhuǎn)換芯片接口。所以本系統(tǒng)可根據(jù)不同的應(yīng)用進(jìn)行擴(kuò)展,進(jìn)一步增強(qiáng)了系統(tǒng)在其他領(lǐng)域應(yīng)用的靈活性。

評論