基于DSP+FPGA的多混沌實時視頻圖像加密系統

2 系統的總體設計

選用TI公司的TMS320C6713 DSP,該款DSP為高性能32位浮點型,其主頻可達到300MHz,處理速度高達2400MIPS,片上共有264k×8位存儲器,內置2個MCASP、2個MCBSP、2個I2C、1組GPIO、2個32位定時器、1個16位主機接口HPI和32位EMIF總線。選用Altera公司CycloneII系列的EP2C5 FPGA,該款FPGA擁有4608個邏輯單元,片上共計119808比特的RAM,2個高性能的鎖相環,13個18×18的硬件乘法器以及具有142個用戶可用的IO口。

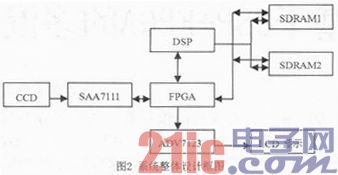

系統的CCD攝像頭直接與視頻解碼芯片SAA7111相連,SAA7111將采集到的模擬圖像數據轉換成RGB565格式的圖像數據,FPGA將接收到的圖像數據存入到SDRAM1,然后發送一個信號給DSP;FPGA同時檢測DSP對SDRAM2的數據加密完了的標志信號,這時FPGA讀取SDRAM2中的數據,將數字圖像數據通過ADV7123轉換模擬圖像數據,通過VGA接口顯示。當DSP得到FPGA發送過來中斷信號后讀取SDRAM1的圖像數據,然后根據多混沌加密算法對其進行加密,然后將加密后的數據存儲到SDRAM1中,同時發送一個加密完成的標志信號給FPGA。系統整體設計框圖如圖2所示。本文引用地址:http://www.104case.com/article/201610/306065.htm

2.1 FPGA子系統設計

FPGA子系統需要實現的功能包括SAA7111的初始化、SDRAM接口控制以及VGA實時顯示模塊。

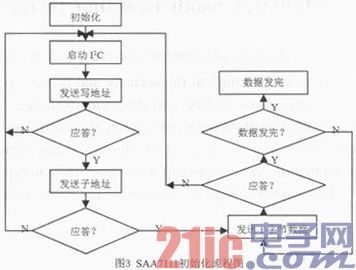

視頻解碼芯片SAA7111在系統的視頻輸入處理部分,需要對其進行合理的配置后,才能實現將模擬視頻信號轉換成相應格式的數字圖像數據。SAA7111片內有32個控制寄存器,其中20個是可編程的,FPGA需通過I2C接口對其進行初始化,初始化流程圖如圖3所示。在對SAA7111進行配置時,首先時鐘信號采用400kHz較為可靠,其次是I2C總線的開始信號、停止信號和應答信號,再次是設置好SAA7111相應寄存器的數據。

SDRAM的主要任務是完成圖像數據的存儲及加密數據輸出。FPGA控制SDRAM程序主要由命令狀態機模塊和數據傳輸2個子模塊組成。系統上電時需有100-200μs的等待時間,然后FPGA對其進行初始化。在進行完初始化之后,便可以對SDRAM進行讀寫控制。對SDRAM進行讀寫操作時,需先激活要讀寫的行和列,才可以對相應的行列進行數據讀寫,讀寫完成后FPGA將對SDRAM產生一個預充電的命令。

FPGA對SDRAM1和SDRAM2是采取乒乓緩存的方式控制。假如這時FPGA對SDRAM1進行存儲圖像數據,寫完數據后對SDRAM2進行讀數據;當FPGA對SDRAM1寫完數據后,DSP讀取SDRAM1里的數據,加密后將數據存入SDRAM1;下一次就是FPGA對SDRAM2進行寫數據,如此反復交叉進行操作。

VGA顯示子模塊主要是產生VGA時序控制信號,VGA時序控制信號主要包括RGB數據信號、行同步信號及場同步信號。

評論