編解碼電路板設計指南

下述注意事項和要求是混合信號電路板設計中非常實用的指導原則。

本文引用地址:http://www.104case.com/article/201610/305336.htm去耦與旁路

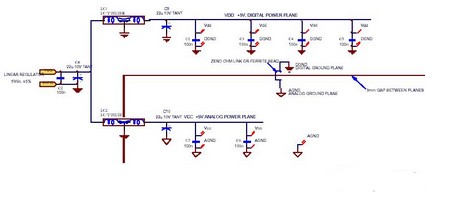

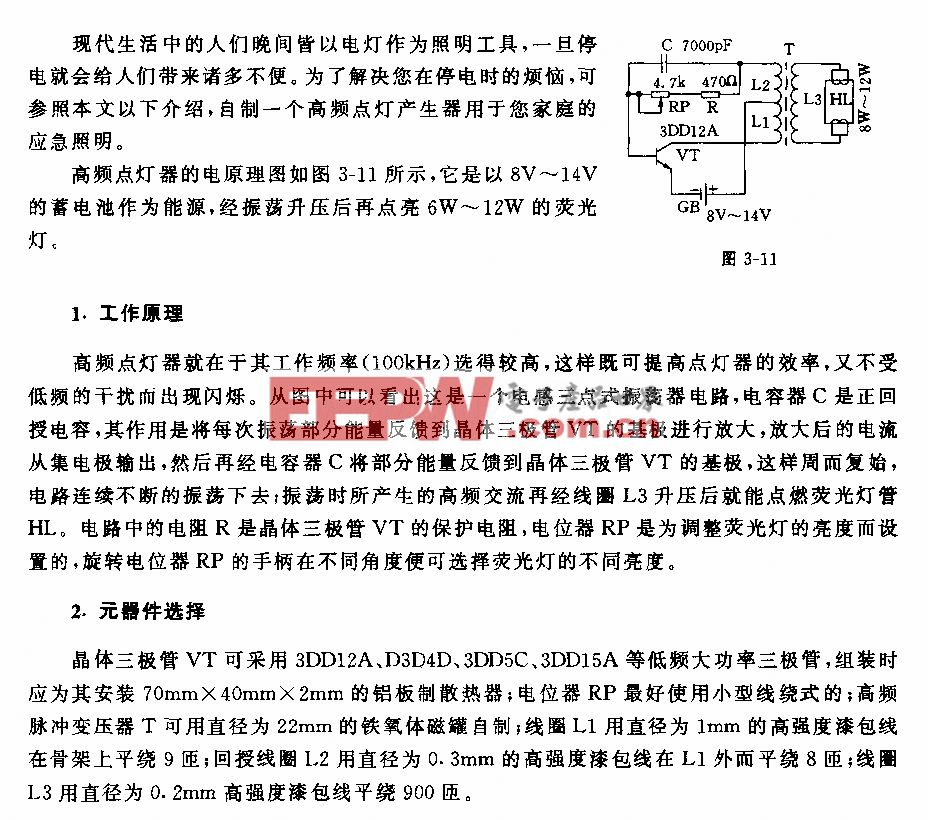

圖 1 為電源去耦與旁路的實例,需要強調的是,在芯片的引腳處(或至少在距離引腳的幾個mm 內)必須安裝低ESL(等效串聯電感)容量為10nF 到100nF 的表面貼裝陶瓷電容。對于普通1oz 銅箔、10mil 寬的印制線有:電感約為1nH/mm,電阻約為2mΩ/mm。

1:混合信號電源、接地和旁路

電源與接地層

要使開關電源遠離ADC 、DAC 和模擬電路。有時,在芯片附近使用一個單獨的5V 三端穩壓器作為模擬電源比較好。在電路板邊緣處加一個22uF 鉭電容或鋁電容有助于降低電源噪聲和去耦扼流元件的ESR(等效串聯電阻)引發的阻尼振蕩。

ADI(Analog Devices) 建議采用接地層原理(數字地與模擬地分開),并且在相應的接地上布置單獨的數字和模擬電源,但不要使層與層之間重疊(避免噪聲的耦合)。兩層之間應有2 mm 到3 mm 的空隙。這就意味著利用四層板包括各接地層和電源層可組成一個內部高電容性夾層結構。這樣,由各自的接地層和電源層構成了一個極其有效、低ESR 和ESL 的旁路電容,其電容量約為5pF/cm2(30pF/in2 )。IC 引腳通過焊盤和過孔直接通向適當的電源層和接地層。所有數字器件安裝在數字電源層和數字接地層的上面;所有模擬器件安裝在模擬電源層和模擬接地層的上面。然而,IC 管腳仍需要加上前面提到的陶瓷旁路電容。這里需要強調,接地層是非常重要和非常有效的,它們優化了混合信號部分的性能,而且還能減少EMI 。

地線層的連接

兩層之間應有單一通道連接,最好在芯片附近使用零歐姆電阻或鐵氧體墊圈。這種連接是完全必要的,它可以避免由于ESD或誤電流(這種誤電流可能流過芯片基底,并可造成破壞性影響。)引起的電位差,同時隔離了高頻電流。對于原型設計,可在多個位置建立可去除的連接,以便調試和測試時與地隔離。此外,不能有任何數字和模擬信號線橫跨過數字層和模擬層的間隙。

在混合信號系統中不可避免地會有信號線橫跨過數字層與模擬層的間隙

數字信號與元件

所有的數字信號與元件應當遠離模擬電路。所有的高速數字信號應當以最短的路徑布線在數字接地層和電源層的上面。

IC插座

避免使用IC 插座。

容性負載

最大限度地減小數字輸出引腳的容性負載。對于長距離的數字信號線,要求負載與其特征阻抗匹配,以避免過沖/欠沖和振蕩。很多應用中特征阻抗Z0約為80Ω,通常用一個82Ω的電阻和一個50pF的電容的RC并聯組合作負載就可以匹配這樣的長距離的數字信號線。

PLD和VLSI邏輯芯片

不要忽視在同一PCB 上相鄰的PLD 和VLSI 邏輯電路芯片,它們往往包含有大量的同步邏輯并產生很大的開關電流,這種開關電流能夠滲透到該電路板的其它部分。解決辦法是保證這些芯片電源引腳有很好的旁路。這種方法既可保證可靠的工作,也能減小電源線上的噪音。

晶體振蕩器(時鐘)的問題

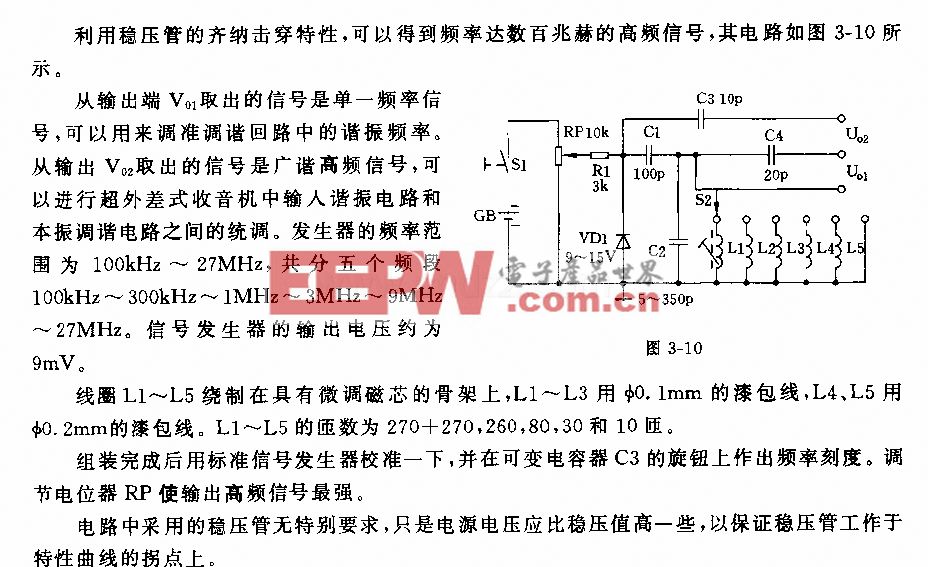

對于ADC和DAC,必需保證取樣去取樣時鐘有足夠純凈的頻譜,也就是要使用低相位噪聲的振蕩器,此振蕩器還要與數字模擬電路部分都分開,因為數字部分干擾影響其頻譜純凈度,而振蕩信號本身又是數字信號,會干擾系統的模擬部分。為獲得更低的相位噪聲,可采用晶體廠家推薦的分立元件(雙極晶體管或FET)晶體振蕩電路(可用一個門來放大振蕩信號,以驅動ADC或DAC),而盡量避免用門與晶體構成的振蕩器。

多個晶體振蕩器可能引起一些問題,如諧波間脈動可能通過其模擬和數字電源或信號以及參考電壓進入編解碼器。可能的話,在同一PCB 上只同時使用一個晶體振蕩器,或者使所需各種頻率都來自單個晶體振蕩器。

磁場

注意電感和變壓器的外部磁場,如有必要,可采用電磁屏蔽元件。RF 去耦扼流線圈可互成直角安裝。電源變壓器應定向安裝在電路板外,并遠離關鍵模擬電路。采用環形電源變壓器可以減弱外磁場。

輸入信號擺幅

要保證偏置電壓、5V CODEC/ADC模擬輸入信號不會超過VCC 或低于接地點,即使是瞬間也應避免。使用低泄漏二極管“箝位”或5V 單軌運算放大器緩沖限制輸入信號擺幅。

EMI/RFI要求

設計時要考慮模擬輸入線和模擬輸出線的EMI/RFI要求。輸入線可能發射和接收RF信號,DAC模擬輸出線則包含高至100MHz的去取樣時鐘的諧波。

普通設計問題

最小化環路面積;最小化公共阻抗;對于容性耦合可采用隔離、屏蔽和低電路阻抗的措施;對于表面和體泄漏可采用隔離措施;對于并行線間耦合,可采用隔離、特征阻抗匹配、用接地層、用地線居中的并行線、用較低速的邏輯電路……

假定

記住:在調試的時候,任何假定(自己認為是對的東西)都值得懷疑!

評論