Intel-鎂光公布25nm NAND細節 采用Airgap技術

在本月6日至8日舉辦的IEDM2010舊金山大會上,Intel與鎂光兩家公司合作展示了其25nm NAND制程的細節,有趣的是,這種制程竟然會是首款將曾被IBM熱捧的AirGap(空氣隙型介電層)技術商用化的產品。

本文引用地址:http://www.104case.com/article/201609/305066.htm

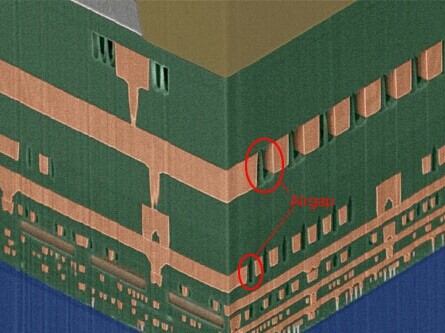

當初IBM用來解釋Airgap的說明圖

必須首先說明的是,Intel和鎂光此前成立了一家NAND合資公司IM Flash,公司此前已經宣布正式將25nmNAND閃存芯片推出上市,不過此前雙方都還沒有透露這款芯片中使用了AirGap技術制作互聯層的介電層。

Chipworks網站的分析師Dick James稱:“這是首款商用化的應用了AirGap技術的產品。”包括IBM公司在內,許多公司都曾經熱捧過這項技術,但該技術在他們的實際產品中均未開花結果。

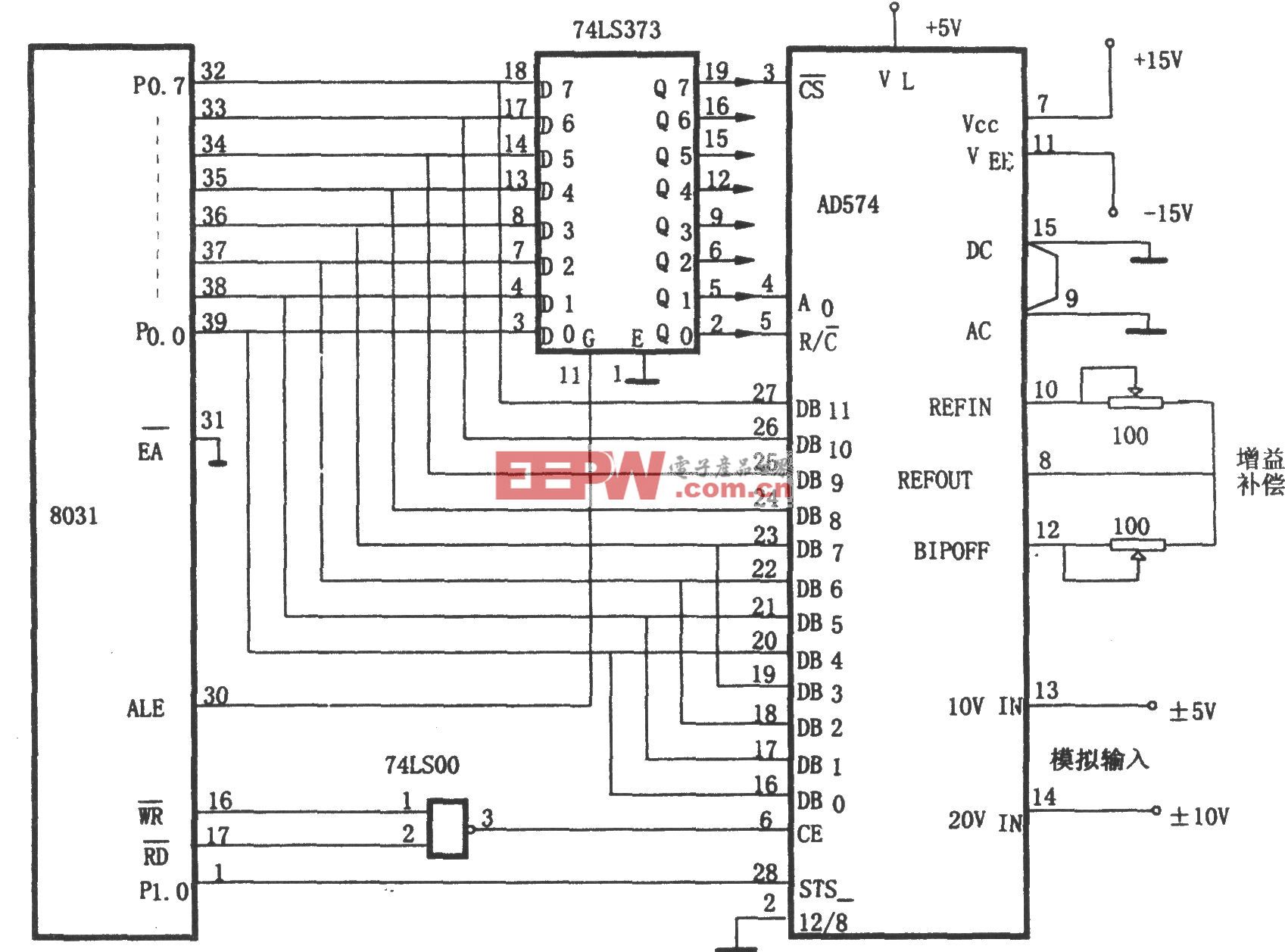

在一份在IDEM上發布的文件中,Intel和鎂光介紹了其64Gb密度的MLC NAND芯片產品,這款產品在芯片字線上的晶體管柵極半節距長度為24.5nm,位線方向上則為28.5nm,晶體管單元的面積為0.0028平方微米。文件中還稱:“晶體管采用液浸式193nm光刻技術,配合了高級柵節距縮減技術,很好地控制了圖形邊緣的線性粗糙度和不同光刻對象關鍵尺寸的變化率。”

文件中還介紹稱:“在25nm尺度,5%的關鍵長度變化率相當于3個晶格位置的長度.由于inhibit操作期間需要隔離6V左右的電壓,因此晶體管功能區的淺槽隔離結構在深度方向上的尺寸很難明顯縮減,這樣產品的淺槽隔離結構的深寬比將高達7:1。而任何結構尺寸上的不一致,都會導致晶體管功能區的彎曲,舉例而言,如果關鍵尺寸變化了3nm,那么溝道的錯位距離可會高達10nm。因此,控制晶體管結構尺寸的穩定性,對保證NAND陣列的良好性能非常重要。過度縮減字線距離,會導致字線間電容的增加和晶體管界面電容的增加。”

文件最后部分寫道:“要解決這個問題,我們引入了空氣隙技術,這種結構將在字線之間生成;同時位線間我們也使用了這種技術。”

說明:Airgap技術即在介電層嵌入空氣隙的技術,其本質與Low-K電介質的性質相同,均是試圖減小導線間電容,提高電路運行速度的技術。

評論