DDS流水線結構的改進

摘要:分析了DDS中流水線結構及輸入數據在其中移動的特點,提出了一種DDS流水線結構的改進方案,給出了實現的方法并作了仿真,分析了對DDS電路性能的改進方案。

本文引用地址:http://www.104case.com/article/201609/304708.htm關鍵詞:DDS 流水線 改進的流水線結構

DDS(Direct Digital Synthesizer)以其頻率分辨率高、轉換速率快及波形變換靈活等特點,已廣泛應用于通訊、雷達、GPS、蜂窩基站有HDTV等領域。DDS相位字長及運算速度決定了DDS的性能[1],相位累加器、移相加法器及LUT的字長越長,頻率分辨率及波形精度越高,相位截尾誤差越小[2]。目前DDS相位累加器的位數一般在32~48位之間;而時鐘頻率越高,輸出頻率的范圍越大。流水線是高速電路中一種常用的技術[3],高速、高精度DDS的相位累加器、相移加法器、用于調幅及正交調制的乘法器都采用了流水線結構。

普通的流水線結構所占用的寄存器資源和其級數的平方比正比,無論是現有的專用DDS集成電路,還是采用FPGA等可編程器件實現,都將占用大量寄存器資源。其實,DDS中的輸入數據一般在一個較長的時間內保持不變。基于這一特點,本文提出一種改進的DDS流水線結構,可以大大減少占用的寄存器資源。

1 問題的提出

1.1 DDS結構及工作原理

圖1是包含移相及調幅部分的相位累加型DDS的結構框圖。每一時鐘周期,N位相位累加器PA與N位頻率控制字FW累加一次。其結果的高M位作波形表LUT(Look-Up Table)的地址,如果加上PSR的值可實現移相,從LUT中讀出D位波形數據送DAC。若乘以AR的值還可實現調幅。改變FW的值可改變輸出頻率,改變PSR的值可實現調相,改變AR的值可以實現調幅。一般情況下,FW、PSR及AR刷新頻率要比DDS系統時鐘慢得多。

1.2 DDS中流水線結構

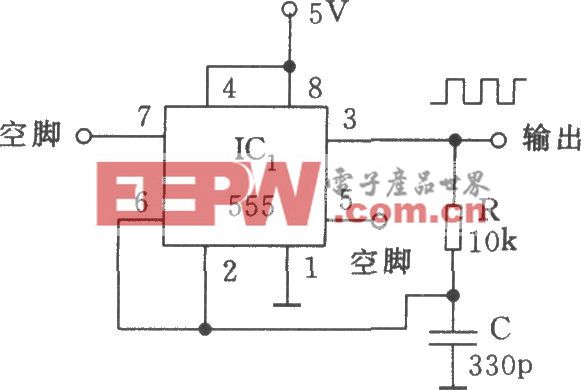

當DDS的相位字長較長、速度較高時,相位累加器、移相加法器或其綜合及調幅乘法器一般都采用流水線結構。以下僅以相位累加器為例,分析流水線的結構、性能及其改進。當相位累加器采用m級n位流水線結構時,有, 這里PA,FW分別是相位累加器的值和相位階距,PAm是各級加法器的部分和。其中,輸入緩沖流水線為m級n位,占用寄存器[(m-1)×m×n]/2 位,而相位累加器輸出的高M位需m1=int[(m-1)/m]+1級流水線,占用[(m1-1) ×m1×n]/2+m1×(M mod m)(int[·]是取整運算)。圖2、3分別是m=4、n=4、M=8時相位累加器的結構及時序圖。此時,輸入流水線占用24位寄存器;m=8、n=4 時(32位相位累加器),輸入流水線占用112位寄存器;m=12、n=4,(48位相位累加器),占用264位寄存器;若選取m=48、n=1,則占用 1128位寄存器。如果省去輸入流水線,改變相位階距時,將導致相位紊亂。

2 改進的流水線結構

2.1 結構及其工作原理

一般來說,DDS控制數據刷新速率遠低于系統時鐘。以相位累加器為例,進入各組加法器的頻率控制字值,只在數據更新后的前m個時鐘周期變化。以后各個周期不再變化。基于這種情況,可以對累加器進行改進,從而節省部分寄存器。圖4是改進輸入流水線的相位累加器結構圖,圖5是輸入數據及控制信號的時序圖。

在輸入數據D0~15(N)準備好后,由外部控制系統向流水線刷新控制電路 CON發出一啟動信號Start,CON在Start下降沿后的第一時鐘上升沿到來時,輸入寫入脈沖WR0,將D0~3(N)寫入第一級流水線寄存器;第二時鐘上升沿到來時,輸出寫入脈沖WR1,將D4~7(N)寫入第二級流水線寄存器;依次類推,到第四上升沿到來時,輸出寫入脈沖WR3,將 D12~15(N)寫入第四級流水線寄存器,完成一次數據的刷新。在以后的周期內,這些數據將保持不變,直至新的Start到來。

改進后的流水線所占用的寄存器位數和相位的字長相等,

與流水線的級數無磁。相位字長較長時,這種改進的效果是非常明顯的。

2.2 刷新控制器的設計

刷新控制器實質上是一種陣發式脈沖分配器,由Start啟動,當完成一個周期的脈沖分配輸出后,便停止計數。陣發式脈沖分配器的設計及實現方法很多,以下是基于Altera的FPGA,以MAX+Plus Ⅱ的HDL實現的陣發式脈沖分配器,流水線中的寄存器為上升沿有效,延遲時間為12.5ns,速度可達80MHz(FLEX 10K20RC240-4),圖6是其仿真結果。

(FLEX 10K20RC240-4),圖6是其仿真結果。

SUBDESIGN control

(cp,start : INPUT;

q3,q2,q1,q0 : OUTPUT;)

VARIABLE

s:MACHINE OF BITS (q3,q2,q1,q0)WITH STATES

(s0=b0000,s1=b0001,s2=b0010,

s3=b0100,s4=b1000);

BEGIN

s.clk = cp;

s.reset = start;

TABLE s=>s;

s0=>s1;s1=>s2;s2=>s3;s3=>s4;s4=>s4;

END TABLE;

END;

2.3 性能改善

2.3.1 寄存器的減少

輸入流水線結構改后后,寄存器的位數和相位累加器的位數呈線性關系,位數大大減少,特別是對級數較多的流水線,即使對寄存器密集型的FPGA,這也是有益的。

2.3.2 功耗降低

由于僅在刷新數據時,流水線中觸發器的狀態發生改變,在以后很長一段時間內,狀態不再改變,這對降低電路功耗是有益的。

2.4 應用

在刷新數據時,只要輸出一個啟動信號,使用方法和方案一樣便捷。啟動信號通常由外部控制電路給出,上例中,

刷新動作從啟動信號Start后的第一個時鐘上升沿開始。

需要注意的是,在刷新數據時,每一組數據保持的時鐘周期數必須大于流水線的級數。上命名中,數據必須保持4個時鐘周期以上,否則高位數據將不能傳送到相應級的累加器。

本文分析了高速DDS中的頻率控制字、相移字等輸入數據的變化特點。提出了一種 DDS流水線結構的改進方案,給出了具體實現的方法及仿真,并成功地用于高頻高精度AWG的研制。用這種方法設計的DDS及NCO等電路,降低了寄存器的占用,也降低了系統的功耗,可有效提高電路的性能價格比。這種設計方法對其它的流水線結構設計也有一定的參考價值。

評論