一種通用基于CPLD實現的CAN接口連接設計

摘要:介紹一種基于CPLD實現的DSP或ARM處理器與CAN總線控制器SJA1000接口連接設計。通常DSP或ARM處理器都有獨立的地址和數據總線,而SJA1000采用的是地址、數據分時復用總線,它們不能直接連接。該設計主要是通過CPLD實現這兩種總線方式的轉接。該方案成本低,性能穩定,實現可靠。采用CPLD使該設計更為自由、靈活。在處理器與CPLD的連接一側是采用微處理器用獨立的地址和數據總線訪問外部存儲器的方式工作的,而許多具有獨立的地址和數據總線的微處理器都能做到訪問外部存儲器,從而使該設計具有很強的通用性。全篇給出了完整詳細的設計代碼和仿真結果,并在實際應用中得到檢驗,可直接應用到設計中。

本文引用地址:http://www.104case.com/article/201609/304285.htm在工業自動化領域,CAN口通信以其卓越的性能、極高的可靠性和低廉的價格得到廣范的應用。Philips公司的SJA1000芯片,是目前使用最為廣泛的一種獨立CAN總線控制器。SJA1000有一系列先進的功能,適合于多種應用,特別在系統優化,診斷和維護方面非常重要。

為了連接到主控制器,SJA1000提供一個分時復用的地址、數據總線和附加的讀寫控制信號。SJA1000可以作為主控制器外圍存儲器映射的I/O器件直接連接到具有Intel方式接口的主控制器。而目前大部分DSP和ARM處理器都是采用獨立的地址和數據總線訪問外部存儲器的,由于時序不相兼容的原因,這些處理器不能直接訪問SJA1000。從而設計一種轉接電路使DSP和ARM處理器能夠連接SJA1000變得很必要。本設計正是解決這一問題。

1 總體設計

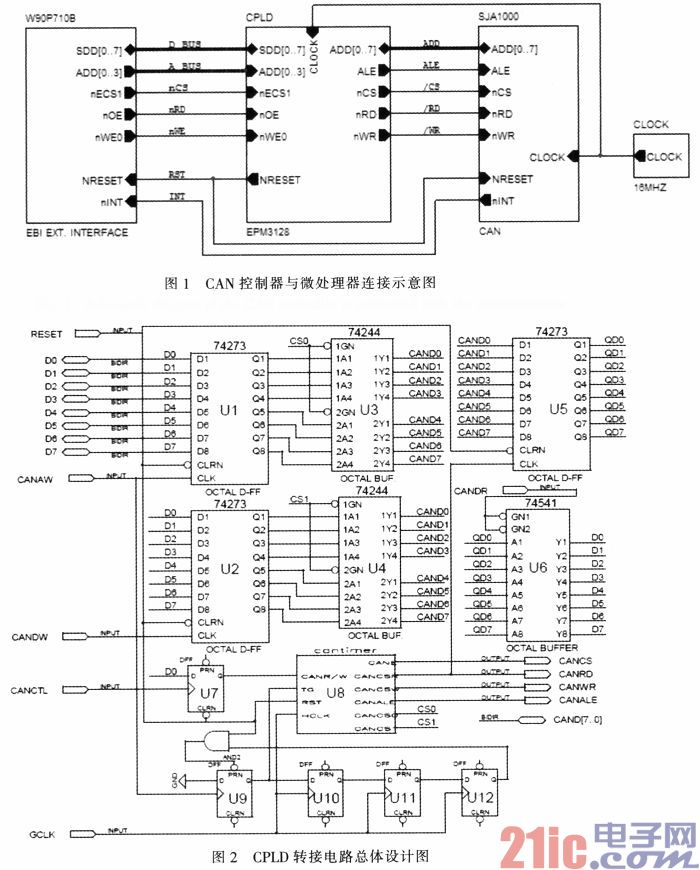

該設計以新塘科技生產的ARM7處理器W90P710B與SJA1000的連接為例,W90P710B采用獨立的地址和數據總線訪問外部存儲器方式工作。圖1表明了CPLD在W90P710B與SJA1000之間的這種轉接關系。

設計中采用的CPLD選用Altera公司的MAX系列可編程邏輯器件EPM3128A芯片。EPM3128A具有128個宏單元,96用戶I/O管腳數,2500個可用門,管腳間延遲快至10ns,計數器速度可高達100 MHz,可以很好的滿足設計需要。本設計采用圖形和AHDL語言混合輸入完成。使用工具為MaxplusⅡ。Ateral公司的MaxplusⅡ,QuartusⅡ,也是業界最著名的CP LD/FPGA開發工具,支持所有的Ateral芯片,如MAX3000,MAX7000,MAX2Ⅱ系列。

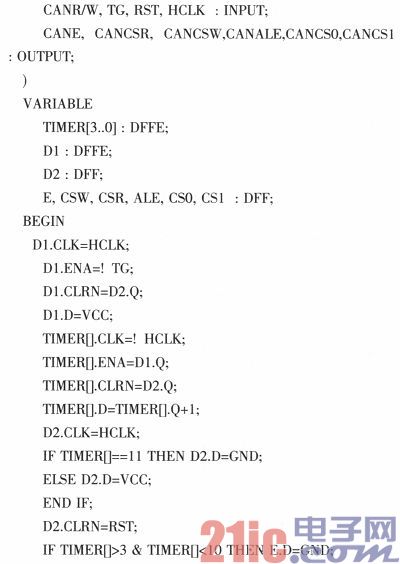

圖2是轉接電路總體設計圖,與ARM處理器連接一側,鎖存器U1用于存儲CAN控制器要訪問的地址,U1的片選信號為CANAW,該信號同時起到啟動時序電路U8輸出讀寫時序的作用;鎖存器U2用于存儲要寫入CAN控制器的數據,U2的片選是CANDW;鎖存器U7的輸出為高,控制U8輸出讀時序對CAN控制器讀取數據,讀出的數據存入U5中,鎖存器U7的輸出為低,控制U8輸出寫時序對CAN控制器SJA1000進行寫操作,將U2中的數據寫入U1所代表的,CAN所在地址中,其片選信號為CANCTL;門電路U6通過片選信號CANDR用以讀取U5中存放的CAN讀出數據。綜上所知,CPLD與ARM處理器接口的是4個寄存器,它們分別是3個寫寄存器:CAN地址寫寄存器CANAW,CAN數據寫寄存器CANDW,CAN控制寄存器CANCTL;一個讀寄存器:CAN數據讀CANDR。ARM就是通過這4個寄存器來操作SJA1000 CAN控制器的。

CPLD與SJA1000連接一側是INTEL方式的標準信號CANCS、CANRD、CANWR、CANALE,這4個信號由時序電路U8產生。U3、U4的輸出,U5的輸入都與SJA1000的數據總線相連,用以接收地址和讀寫數據。

復位信號RESET使系統上電時處于初始狀態。時鐘信號GCLK取8 MHz,由SJA1000的16 MHz時種2分頻得來。U9-U12用以延寬CANAW對U8的低電平啟動脈沖,使U8工作的更可靠。整個設計占用ARM4個地址和一個中斷資源,只要有足夠的地址和中斷源ARM就可按此設計擴充出多個CAN口。

2 時序電路設計

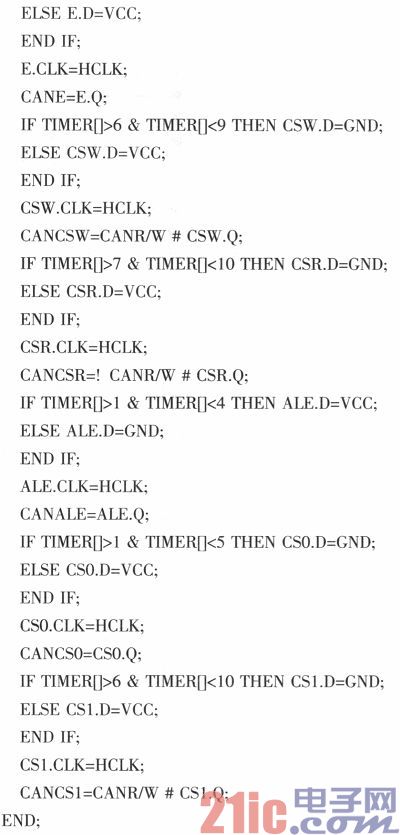

CAN讀寫時序電路U8的設計輸入采用AHDL語言,其電路符號如圖3所示。

U8的設計代碼如下:

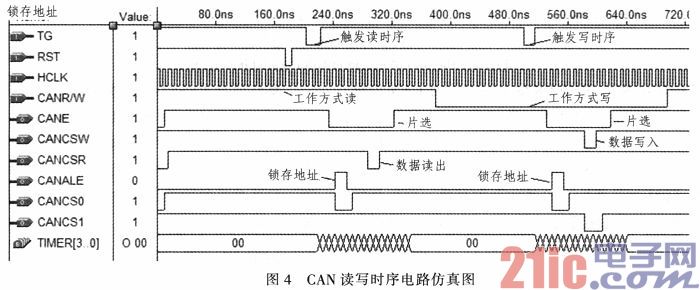

其波形仿真結果如圖4所示。

3 轉接電路工作原理介紹

CAN讀寫時序電路U8是整個設計的核心,它起到對SJA1000進行讀寫操作的作用。

當ARM處理器要對SJA1000進行讀操作時,它先通過CANCTL片選在U7中寫入‘1’高電平,使U8工作在讀的狀態,然后把要讀的地址通過片選CANAW寫入U1,片選CANAW還啟動了U8的TG觸發信號(圖4的前半部分、CANE為低與CANR/W為高的那部分),使U8的CANE(即CANCS)輸出低電平,CANCS0輸出低脈沖打開門電路U3,使CAN地址出現在SJA1000的總線上,同時CANALE出現一個正脈沖,將該地址鎖存到SJA1000的地址寄存器中,隨后CANCSR(即CANRD)輸出低電平對SJA1000進行讀數據,在CANCSR低電平脈沖結束的上升沿處出現SJA1000總線上的數據被鎖存到U5寄存器中,然后CANE變高,讀時序完成。隨后ARM處理器通過CANDR片選打開門U6將數據讀走。

當ARM處理器要對SJA1000進行寫操作時,它先通過CANCTL片選在U7中寫入‘0’低電平,使U8工作在寫的狀態,然后再把要寫的數據通過片選CANDW寫入U2,最后把要寫的地址通過片選CANAW寫入U1,片選CANAW還啟動了U8的TG觸發信號(圖4的后半部分、CANE與CANR/W同時為低的那部分),使U8的CANE(即CANCS)輸出低電平,CANCS0輸出低脈沖打開門電路U3,使CAN地址出現在SJA1000的總線上,同時CANALE出現一個正脈沖,將該地址鎖存到SJA1000的地址寄存器中,隨后CANCS1輸出低脈沖打開門電路U4,使CAN要寫入的數據出現在SJA1000的總線上,同時CANCSW(即CANWR)輸出低電平對SJA1000進行數據寫入,然后CANE變高,寫時序完成。

評論