PCIe 4.0即將跨出實驗室

盡管PCI Express (PCIe) 4.0訴求16GT/s傳輸速率的規格要到明年才底定,但已有幾款采用PCIe 4.0架構的晶片即將投片。一旦PCIe 4.0版的所有細節發布,PCI SIG組織的目標將積極展開傳輸速率高達25或32GT/s的5.0新版任務。

本文引用地址:http://www.104case.com/article/201606/293331.htm在日前于加州舉行的PCI SIG年度開發者大會上,包括Cadence、PLDA和Synopsys等業界廠商展示其PCIe 4.0實體層、控制器、交換器以及其他IP模組等產品規劃,包括一款采用PCIe 4.0規格的100 Gbit/s Infiniband交換器晶片。

下一代5.0傳輸規格:25或32 Gbits/s?

從PCI SIG批準最近的標準——8GT/s傳輸速率的PCIe 3.0版,已經有6年多的時間了。在展開4.0版本時,PCI SIG認為它應該會是最后一版采用銅纜的晶片至晶片互連規格了。然而,從那時起,乙太網路(Ethernet)與Fiber Channel陣營分別將銅互連技術推向了25和32 Gbits/s的傳輸速率。

“我們知道必須推進PCIe至下一代,只是還需要解決一些細節,”PCI SIG主席Al Yanes表示。

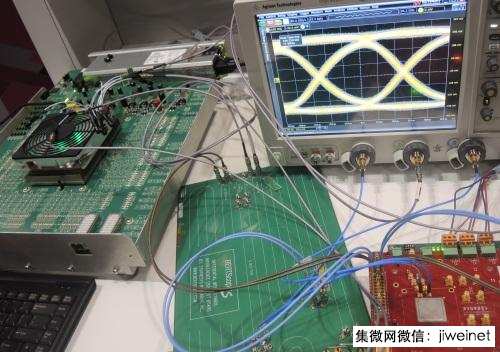

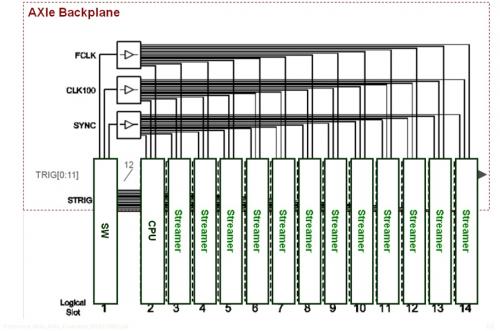

Cadence展示其Mellanox 100G Infiniband交換器晶片(左),采用PCIe 4.0跨越背板(中央)連接至控制器(紅色PCB右側)

“我們不能再玩編碼的把戲了,”Yanes指出,相較于前一代采用的8b/10b編碼技術,3.0版采用更高效的128b/130b編碼機制。“但再進一步升級至256b編碼方案,除了頻率提高以外,并不能帶來更多功能。”

需求就來自于普遍的預期。例如,網卡已經達到100Gbit/s的速率,接下來將會需要更快速的晶片互連,就像下一代繪圖處理器與固態硬碟(SSD)一樣。

對于擁有732家公司成員的組織來說,要建立一個適于從智慧型手機到超級電腦等一切應用的標準并不容易。隨著資料速率增加以及訊號余裕縮漸,推出新版PCIe之間的時間已經從3年延長到7年了。

搭載PCIe 4.0介面規格的幾款晶片即將投片,Mellanox的交換機晶片就是其中之一

法國公司PLDA展示采用其FPGA交換機晶片的PCIe 4.0測試板

PCIe 4.0踏出第一步

0.7版的PCIe 4.0標準目前正在審核中,預計在下個月完成。接下來,工程師將針對0.9版展開一連串的實驗室測試,以驗證該規格的所有功能和參數。預計在2017年4月完成1.0標準。

該組織在一年前指出,希望能在2015年底前完成0.7草案中,并使其成為包含各種新功能的最后一個版本。“要讓組織中的所有成員具有共識,所花的時間比預期的更久,”Yanes表示。

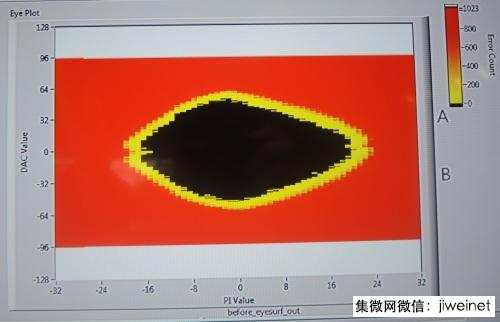

在核準的功能中特別棘手的是所謂的“通道建模”(channel modelling),它可以讓系統工程師檢查眼圖以及確認互連的每一通道,以掌握其設計存在多少余量。

“4.0規格已經存在很長一段時間了。我們有許多客戶準備在今秋投片采用這一介面規格的產品,因為他們知道目前的0.7版草案已經夠好了,”Synopsys IP部門產品行銷經理Scott Knowlton表示。

Cadence和Synopsys展示執行于其工作站IP功能區塊的PCIe 4.0通道建模特性

“我們有一個客戶最近投片串列解串器(serdes),他們覺得已經等待夠久了,不能錯過這一市場,因此,相關產品很快就能在市場上看到,相容性計劃也將隨之而來,”Cadence IP部門的一位PCI專家Arif Khan表示。

在今年稍早,IBM宣布其下一代伺服器處理器Power9的規格,其中包括計劃支援PCIe 4.0。

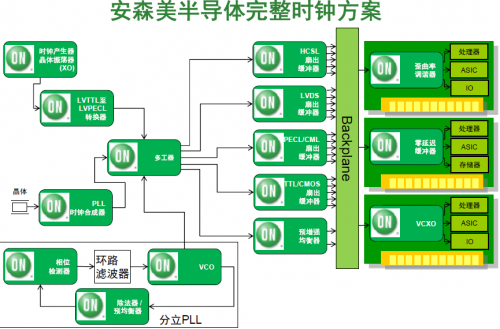

為了達到更快的數據速率,4.0版的傳輸距離必須有所折衷,約為12-14英寸。因此,在3.0版開始普遍的重定時器(retimer)與訊號中繼器(redriver)將會更加被廣泛使用。

在此次大會上,Cadence和Synopsys都展示了可用于晶片IP功能區塊的通道建模功能。Cadence的晶片采用16nm FinFET制程,而Synopsys則宣稱其功能區塊可較前一代PCI功能區塊降低達20%的延遲,面積也減少了15%。

Pericom展示PCIe用12 Gbit/s訊號中繼器,成本約為重定時器的四分之一,該公司并預計要再過一、兩年才可看到16 Gbit/s規格的新款訊號中繼器

評論