基于GaN FET的CCM圖騰柱無橋PFC

D.安全GaN FET

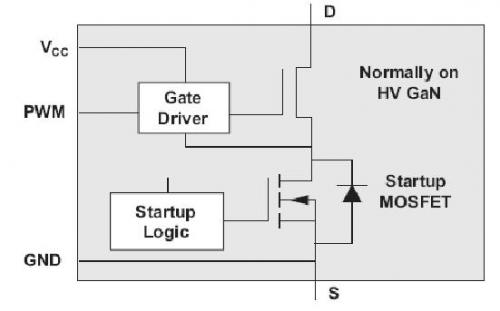

本文引用地址:http://www.104case.com/article/201605/291322.htm為了克服共源共柵結構的缺點,我們在這里介紹一個全新的安全GaN FET結構(如圖6中所示)。

圖6—安全GaN FET結構。

這個安全GaN FET集成了一個常開型GaN器件、一個LV MOSFET、一個啟動電路和一個用于GaN器件的柵極驅動器。MOSFET的功能與其在GaN共源共柵FET結構中的功能一樣。它確保常開型GaN器件在Vcc偏置電壓被施加前關閉。在Vcc被施加,并且柵極驅動器建立一個穩定的負偏置電壓后,啟動邏輯電路將MOSFET打開,并在隨后保持接通狀態。由于GaN器件不具有少數載子,也就不存在反向恢復,與相對應的MOSFET相比,GaN的柵極電容要少10倍,輸出電容要低數倍。安全GaN FET完全涵蓋了GaN所具有的優勢。出色的開關特性確保了全新的開關轉換器性能等級。還應指出的一點是,由于安全GaN FET內沒有實際存在的體二極管,當一個負電流流經GaN FET,并且在漏極和源極上產生出一個負電壓時,這個GaN器件的運行方式與二極管一樣。GaN FET在Vds達到特定的閥值時開始反向傳導,而這個閥值就是“體二極管”正向壓降。正向壓降可以很高,達到數伏特。有必要接通GaN FET來減少二極管模式下運行時的傳導損耗。

III.圖騰柱PFC CCM控制

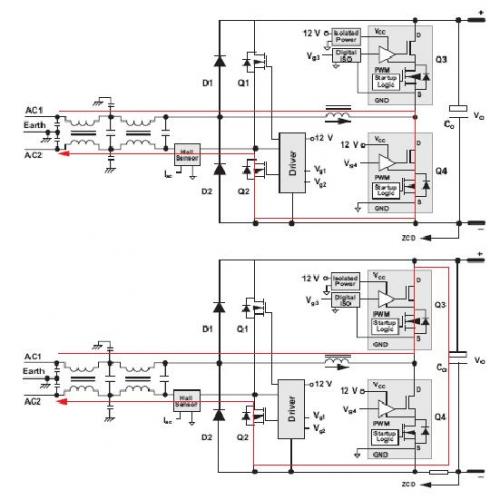

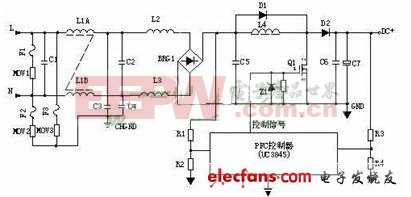

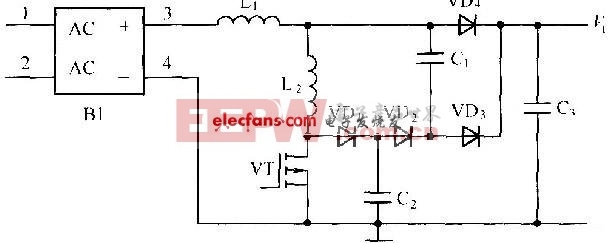

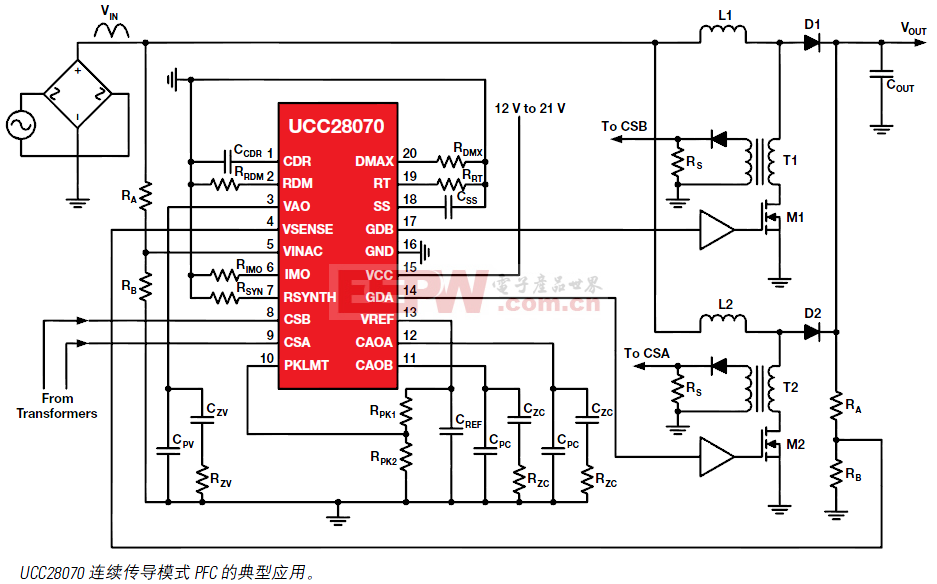

圖騰柱PFC是一款不錯的測試工具,可以在硬開關模式中對安全GaN FET進行評估。圖7中所示的是一個常見的圖騰柱PFC電源電路。Q3和Q4是安全GaN FET;Q1和Q2是AC整流器FET,它在AC線路頻率上開關;而D1和D2是浪涌路徑二極管。當AC電壓被輸入,并且Vac1-Vac2處于正周期內,Q2被接通時,Q4運行為一個有源開關,而Q3運行為一個升壓二極管。為了減少二極管的傳導損耗,Q4在同步整流模式中運行。而對于負AC輸入周期,此電路的運行方式一樣,但是具有交流開關功能。

圖7—有源開關周期(上圖)和續流周期(下圖)中,正AC輸入下,圖騰柱PFC的工作方式。

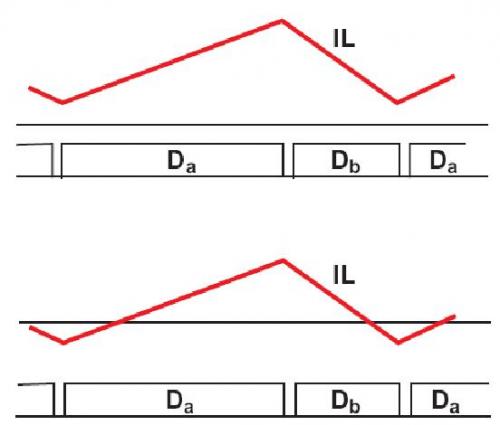

正如在第II部分中描述的那樣,這個“體二極管”具有一個很明顯的正壓降。這個GaN FET應該在續流期間被接通。為了實現CCM運行,在插入特定的死區時間的同時,有源FET和續流FET分別在占空比D和1-D內開關。如圖8中所示,在重負載下,電感器電流可以全為正,不過在輕負載情況下,這個電流可以變為負。

圖8—重負載(上圖)和輕負載(下圖)情況下的PFC電感器電流。

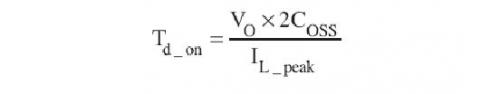

特定的負電流對于軟開關有所幫助,但是,過高的負電流會導致較大的循環功率和低效率。為了實現最優效率,GaN FET的接通和關閉死區時間需要根據負載和線路情況進行實時控制。由于GaN FET輸出電容,Coss,不會隨Vds電壓的波動而大幅變化,從有源FET關閉到續流FET接通的死區時間Td-on可以計算為,

在這里,Vo是PFC輸出電壓,而IL-peak是峰值電感器電流。

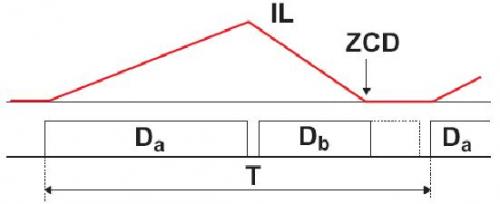

在CCM模式下,被定義為續流FET關閉到有源FET接通的死區時間Td-off應該盡可能保持在較小的水平。如圖9中所示,當接收到零電流檢測 (ZCD) 信號后,相應的PWM隨之被斬波,以避免出現一個負電流和循環功率。這樣的話,GaN FET運行為一個理想二極管,這通常被稱為理想二極管仿真 (IDE)。

圖9—理想二極管仿真控制。

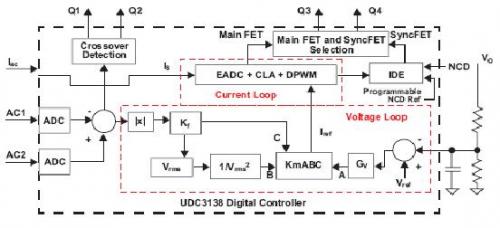

為了用理想二極管仿真實現CCM控制,我們選擇的是UCD3138,一款融合數字控制器。這個控制器塊的功能如圖10中所示。PFC的電壓環路和電流環路分別由固件和硬件CLA執行。通過采用將ZCD用作觸發信號的一個控制器內部逐周期 (CBC) 硬件,可以實現IDE。

圖10—用于圖騰柱PFC控制的UCD3138。

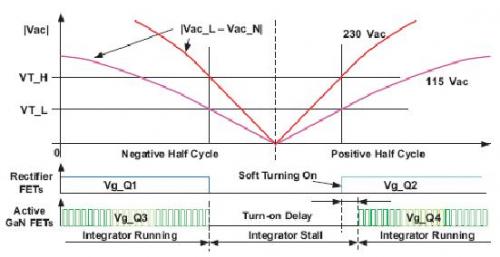

為了最大限度地減少AC輸入整流器二極管的傳導損耗,如圖7中的Q1和Q2所顯示的那樣,常常用低Rds_on MOSFET替換低速整流器二極管。這些MOSFET和高速GaN FET,Q3和Q4,根據AC電壓交叉點檢測值,在正負AC輸入周期之間變換工作狀態。這個任務看似簡單,但是,為了實現潔凈且平滑的AC交叉電流,應該將很多注意事項考慮在內。交叉檢測的精度對于保持正確的工作狀態和運行十分重要。這個精度經常受到感測電阻器容差和感測電路濾波器相位延遲的影響。幾伏特的計算錯誤會導致很大的電流尖峰。為了避免由整流器FET提前接通所導致的輸入AC短路,必須要有足夠的消隱時間讓Q1和Q2關閉,并且應該將這個時間插入到檢測到的交叉點上。消隱時間的典型值大約在100µs至200µs之間。由于MOSFET的輸出電容,Coss,很明顯,Q1和Q2上的電壓應該在消隱時間內幾乎保持恒定。在互補整流器FET被接通前,PFC保持在之前的運行狀態中,此時,施加到升壓電感器上的電壓幾乎為零,而有源GaN FET運行在幾乎滿占空比狀態下。在這一點上,接通互補整流器FET,或者在有源開關和同步開關之間變換GaN FET的這兩個功能,會在升壓電感器中形成大電壓二次浪涌,并因此導致一個較大的電流尖峰。理論上,在理想AC電壓交叉點上同時改變整流器FET和GaN FET工作狀態可以避免電流尖峰,并且保持電流環路的負反饋,不過,這在實際環境中很難實現。此外,任何由突然狀態變化所導致的電流尖峰會干擾電流環路,并且導致一定的電流振鈴級別。[9] 建議在交叉點上使用PFC軟啟動。顧慮在于,AC交叉檢測電路通常具有相位偏移,并且有可能不夠精確。過早或過晚的改變狀態會導致AC線路短路,或者電流環路正反饋,這會形成電流尖峰。這篇文章內提出的一款全新可靠的控制機制就是為了確保一個平滑的狀態改變。圖11顯示的是狀態變化的時序圖。

圖11—PFC狀態變化時序圖。

輸入AC線路電壓VAC_L和中間電壓VAC_N被分別感測。得出的兩個感測到電壓的差值被用于AC電壓交叉檢測,這實際上是一個差分感測機制。它消除了Y_Cap電流對感測精度的影響。VAC_L-VAC_N的符號被用來確定輸入的正周期和負周期。VAC_L-VAC_N的絕對值與高壓線路的AC電壓交叉閥值VT_H,以及低壓線路的VT_L進行比較,以確定AC電壓是否處于交叉區域內。如果回答是肯定的,整流器FET和升壓開關均被關閉,而控制環路的積分器被暫停。當AC電壓增加,并且存在于交叉區域內時,相應的整流器FET被緩慢接通。通過插入一個適當的值柵極電阻器,可以限制接通速度。在整流器FET被接通后,一個短延遲,比如說20µs,在積分器被暫停,并且PWM輸出被再次啟用前被插入。

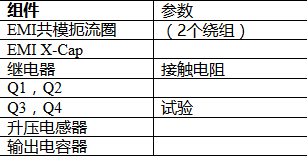

IV.實驗

為了評估安全GaN FET的性能,并驗證CCM圖騰柱PFC控制機制,一個運行頻率為140kHz的750W PFC電路被設計成一個測試工具。表2中列出了這個電路的主要組件參數。

表2—750W PFC電路主要組件參數。

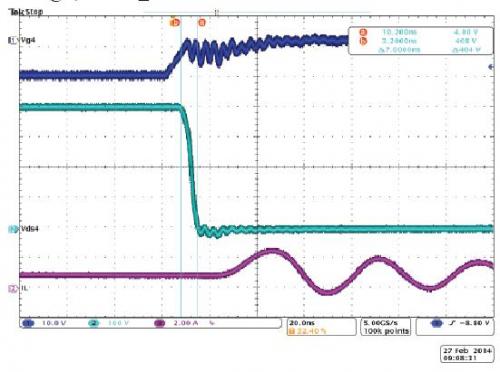

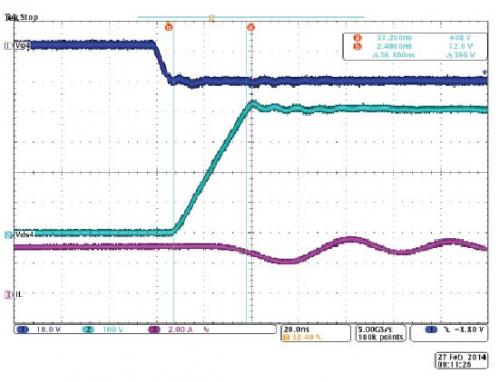

圖12和圖13顯示的是D-mode GaN FET接通和關閉波形。Vg4是柵極驅動器信號,Vds是漏源電壓,而IL是升壓電感器電流。

圖12—GaN FET接通波形。

圖13—GaN FET關閉波形。

如這些圖中所見,GaN FET在dv/dt的值達到79V/ns最大值時的接通時間為7ns。可以在開關結束時觀察到大約10-20V的振鈴。這個振鈴由H橋跟蹤泄露電感和H橋輸出高頻陶瓷電容器的諧振所導致。在關閉時,Vds緩慢上升,過沖電壓大約為20V。dv/dt受到GaN FET輸出電容值的限制。零GaN“體二極管”正向恢復特性最大限度地減小了電壓過沖幅度。

評論