用于高頻接收器和發(fā)射器的鎖相環(huán)-第三部分

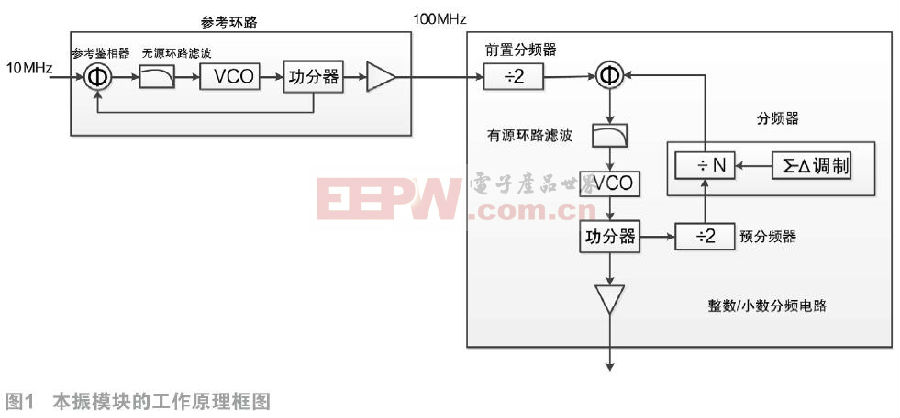

本系列第一部分介紹了鎖相環(huán)(PLL),說明了其基本架構(gòu)和工作原理。 另外舉例說明了PLL在通信系統(tǒng)中的用途。 在第二部分中,我們詳細考察了相位噪聲、參考雜散、輸出漏電流等關(guān)鍵性能規(guī)格,還考慮了它們對系統(tǒng)性能的影響。 在本部分中,我們將考察PLL頻率合成器的主要構(gòu)建模塊。 我們還將比較整數(shù)N和小數(shù)N架構(gòu)。 最后將總結(jié)市場上現(xiàn)有的VCO,同時列出ADI的現(xiàn)有頻率合成器系列。

本文引用地址:http://www.104case.com/article/201605/290712.htmPLL頻率合成器基本構(gòu)建模塊

PLL頻率合成器可以從多個基本構(gòu)建模塊的角度來考察。 我們在前面已經(jīng)提到過這個問題,下面將更加詳細地進行探討:

鑒頻鑒相器(PFD)

參考計數(shù)器(R)

反饋計數(shù)器(N)

鑒頻鑒相器(PFD)

頻率合成器的核心是鑒相器,也稱鑒頻鑒相器。 在鑒相器中,將比較參考頻率信號與從VCO輸出端反饋回來的信號,結(jié)果得到的誤差信號用于驅(qū)動環(huán)路濾波器和VCO。 在數(shù)字PLL (DPLL)中,鑒相器或鑒頻鑒相器是一個邏輯元件。三種最常用的實現(xiàn)方法為:

異或(EXOR)柵極

J-K觸發(fā)器

數(shù)字鑒頻鑒相器

這里,我們只考慮PFD,這也是ADF4110和ADF4210頻率合成器系列中使用的元件,因為與EXOR柵極和J-K觸發(fā)器不同,處于解鎖狀態(tài)時,其輸出為頻差以及兩個輸入間相差的函數(shù)。

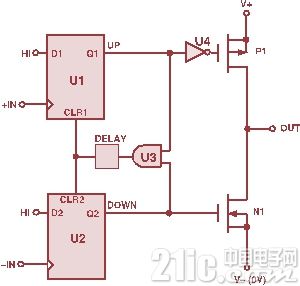

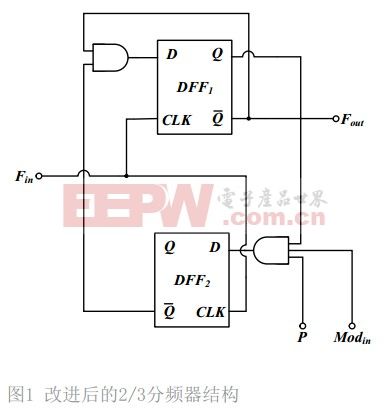

圖1所示為PFD的一種實現(xiàn)方案,該類器件基本上由兩個D型觸發(fā)器組成。 一路Q輸出使能正電流源,另一路Q輸出則使能負電流源。 假設本設計中D型觸發(fā)器由正邊沿觸發(fā),則狀態(tài)為(Q1, Q2):

11—兩個輸出均為高電平,由反饋至觸發(fā)器上CLR引腳的AND柵極(U3)禁用。

00—P1和N1均關(guān)閉,輸出OUT實際處于高阻抗狀態(tài)。

10—P1開啟,N1關(guān)閉,輸出位于V+。

01—P1關(guān)閉,N1開啟,輸出位于V–。

圖1. 運用D型觸發(fā)器的典型PFD。

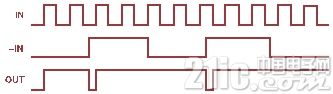

現(xiàn)在考慮系統(tǒng)失鎖且+IN處的頻率遠高于–IN處的頻率時電路的性能表現(xiàn),如圖2所示。

圖2. PFD波形(鎖頻和鎖相均解除)。

由于+IN處的頻率遠高于–IN處的頻率,因此輸出多數(shù)時間處于高電平狀態(tài)。 +IN上的第一個上升沿會發(fā)送輸出高電平,并且這種情況會一直持續(xù)到–IN上出現(xiàn)第一個上升沿。在實際的系統(tǒng)中,這就意味著輸出及VCO的輸入會被進一步拉高,進而造成–IN處的頻率增加。這恰恰是期望達到的效果。

如果+IN處的頻率遠低于–IN處的,則會出現(xiàn)相反效果。 OUT處的輸出多數(shù)時間處于低電平狀態(tài)。 這會在負方向上驅(qū)動VCO,并再次使得–IN處的頻率更加接近+IN處的頻率,從而達到鎖定條件。 圖3顯示了輸入處于鎖頻和接近鎖相條件時的波形。

圖3. PFD波形(鎖頻,但相位鎖定解除)。

由于+IN領(lǐng)先于–IN,因此輸出為一系列正電流脈沖。 這些脈沖往往會驅(qū)動VCO,使得–IN信號變得與+IN信號相位對齊。

發(fā)生這種情況時,如果U3和U1及U2的CLR輸入端之間沒有任何延遲元件,那么輸出可能會進入高阻抗模式,從而既不會生成正電流脈沖,也不會生成負電流脈沖。 這并不是一種很好的狀況。 VCO會發(fā)生漂移,直到造成顯著的相位誤差并再次開始生成正電流脈沖或負電流脈沖。 這種循環(huán)會持續(xù)相當長的一段時間,其影響是電荷泵的輸出會被某個信號(PFD輸入?yún)⒖碱l率的次諧波)調(diào)制。 由于這可能是一種低頻信號,因此無法通過環(huán)路濾波器進行衰減,從而會導致VCO輸出頻譜中出現(xiàn)非常明顯的雜散,該現(xiàn)象稱為“間隙”效應。 通過在U3的輸出端和U1及U2的CLR輸入端之間添加延遲元件,可以確保不會發(fā)生這種情況。 添加延遲元件后,即使+IN和–IN相位完全對齊時,電荷泵輸出端仍會生成電流脈沖。 該延遲的持續(xù)時間等于在U3輸出處插入的延遲,稱為反沖防回差脈沖寬度。

參考計數(shù)器

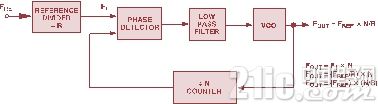

在傳統(tǒng)的整數(shù)N分頻頻率合成器中,輸出頻率的分辨率由施加于鑒相器的參考頻率決定。 因此,舉例來說,如果需要200 kHz間距(如GSM電話中),那么參考頻率必須為200 kHz。 但是,獲取穩(wěn)定的200 kHz頻率源并不容易。 一種合理的做法是采用基于晶振的良好高頻源并對其進行分頻。 例如,從10 MHz頻率基準開始并進行50分頻,就可以得到所需的頻率間隔。這種方法如圖4所示。

圖4 在PLL頻率合成器中使用參考計數(shù)器。

反饋計數(shù)器N

N計數(shù)器也稱為N分頻器,是用于設置PLL中輸入頻率和輸出頻率之間關(guān)系的可編程元件。 N計數(shù)器的復雜性逐年增長。 除簡單的N計數(shù)器之外,經(jīng)過發(fā)展,后來還包括“預分頻器”,后者可具有“雙模”。

這種結(jié)構(gòu)已經(jīng)發(fā)展成為下列情況下固有問題的一種解決方案:需要超高頻輸出時使用基本N分頻結(jié)構(gòu)來反饋至鑒相器。 例如,我們假設需要一個間距為10 Hz的900 MHz輸出。 可以使用10 MHz參考頻率并將R分頻器設為1000。然后,反饋中的N值必須為90,000。這意味著,至少需要一個能夠處理900 MHz輸入頻率的17位計數(shù)器。

為處理此范圍,需要考慮在可編程計數(shù)器之前加上一個固定計數(shù)器元件,以便將超高輸入頻率拉低至標準CMOS的工作頻率范圍內(nèi)。 該計數(shù)器稱為預分頻器,如圖5所示。

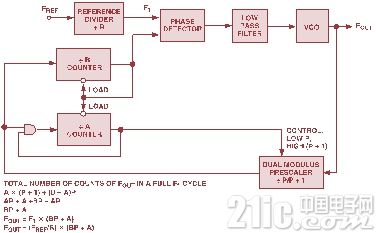

然而,使用標準的預分頻器會導致其他并發(fā)癥。 現(xiàn)在,系統(tǒng)分辨率降低(F1 × P)。 可通過使用雙模預分頻器來解決這個問題(圖6)。 這種方法可以享有標準預分頻器種種優(yōu)勢,又不會犧牲系統(tǒng)分辨率。 雙模預分頻器是一種可通過外部控制信號將分頻比從一個值切換為另一個值的計數(shù)器, 通過使用帶有A和B計數(shù)器的雙模預分頻器,仍可以保持F1的輸出分辨率。 不過,必須滿足下列條件:

圖5. 基本預分頻器。

圖6. 雙模預分頻器。

1.如果兩個計數(shù)器未超時,其輸出信號都為高電平。

2.當B計數(shù)器超時時,其輸出變?yōu)榈碗娖剑⒘⒓磳蓚€計數(shù)器加載至其預設值。

3.加載到B計數(shù)器的值必須始終大于加載到A計數(shù)器的值。

假設B計數(shù)器剛發(fā)生超時并且兩個計數(shù)器均已經(jīng)重新加載值A(chǔ)和B。我們來看看再次達到相同狀態(tài)所需的VCO周期數(shù)。

只要A計數(shù)器未超時,預分頻器即會以P + 1進行分頻。因此,每次預分頻器計數(shù)達到(P + 1)個VCO周期時,A和B計數(shù)器都會遞減1。 這意味著,A計數(shù)器會在((P + 1) × A)個VCO周期后超時。 然后,預分頻器會切換至P分頻。也可以說,此時B計數(shù)器還有(B – A)個周期才會超時。 所需時間為: ((B – A) × P)。 現(xiàn)在,系統(tǒng)會返回到剛開始的初始條件。

所需的VCO周期總數(shù)為:

N = (A × (P + 1)) + ((B – A) × P)

N = (A × (P + 1)) + ((B – A) × P)

= AP + A + BP – AP

= AP + A + BP – AP

= A + BP

= A + BP

評論