基于FPGA的掃頻信號源的研究與設計

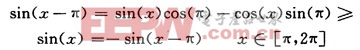

sin(x)函數在0~2π區間內,它是關于x=π的奇函數。即:

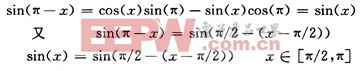

所以只需將0~2π區間的相位編碼減去π,求出其幅度值后在加移負號,這樣的效果就相當于直接對π~2π區間相位求sin值。這個負號要以數字編碼的形式表現出來,所以,π~2π區間的幅度序列是0~π區間幅度序列的補碼。在0~π區間,sin(x)函數是關于x=π/2的偶函數。所以:

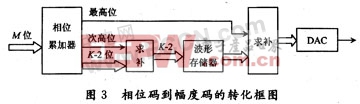

可見,當相位處于π/2~π區間時,將此時的相位編碼減去π/2后,在以π/2為模對其求補,這樣得到的相位值就是處于0~π/2區間并和原相位值有相同的函數值,在以這個相位碼對ROM尋址,得出的幅度就是π/2~π區間對應幅值序列。即ROM中只存儲0~π/2的幅度序列,然后通過相位求補,獲得0~π的幅度碼,通過幅度求補獲得π~2π的幅度碼。優化后的相位碼到幅度碼的轉化框圖如圖3所示。

這樣就完成了整個波形的拼接,實現用ROM只存儲1/4周期波形而可以輸出整個周期,減少了ROM的2位地址,ROM表壓縮比達到了4:1,且硬件電路比較容易實現。

3 信號調理電路

信號調理電路包括低通濾波器和功率放大2部分。

經過D/A轉化輸出信號含有高頻噪聲,故要對其進行濾波處理,濾除不需要的頻率分量,以便輸出頻譜純凈的正弦信號。本系統選用7級橢圓低通濾波器,其截止頻率為9.8 MHz。功率放大部分是為了提高掃頻信號源驅動后級負載的能力。該放大電路選用高速寬帶運放MAX 4117及三極管2N2905,2N2219,其帶寬可達到300 Mb/s,輸入輸出阻抗均為50 Ω。

4系統性能及測試結果

本系統采用Altera公司的EP2C20F484C8為主控制器,D/A轉換器選用AD公司的AD9761,AD9761是一個雙通道,具有40 MSPS的精度為10位的高速CMOS DAC,并內置2倍數插值FIR濾波器。

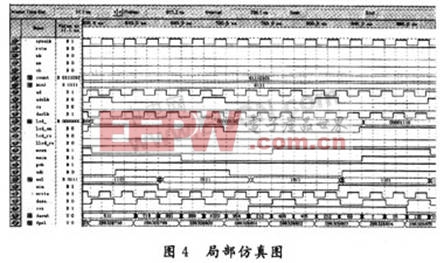

在QuartusⅡ中進行時序仿真,系統的局部仿真結果如圖4所示。

通過QuartusⅡ中的嵌入式邏輯分析儀SignalTapⅡ分析結果如圖5所示。

測試結果表明,本系統設計的掃頻信號源在線性掃頻模式下,完全達到了預期的設計目的。

系統最終在硬件電路中測試結果如下:最大掃頻范圍:DC~10 MHz,掃頻寬度可在此范圍內任意設定;最小掃頻步長:50 Hz;掃頻速度:100 Hz/s;輸出波形幅值范圍:0~5 V;幅值分辨率:50 mV。

5 結語

本掃頻信號源采用DDS技術,完成對相位累加器和相位幅度轉化電路的優化設計,與相比利用FPGA芯片將掃頻信號源的硬件電路集成在一個片上系統,提高整個系統的工作頻率,并減少了寄存器的占用數量。

所有電路模塊采用Verilog HDL語言進行RTL級描述,并完成邏輯綜合、布局布線、時序仿真及硬件測試,最終在硬件電路上驗證了整個系統設計的正確性。測試結果表明,該掃頻信號源的時鐘頻率可以穩定的運行于50 MHz,信號源的頻率分辨率可以達到0.1 Hz,掃頻范圍可以在0~10 MHz之間任意設定,完全滿足在中低端掃頻儀中應用的要求。

電機保護器相關文章:電機保護器原理

評論