基于USB的高精度多通道數據采集卡設計

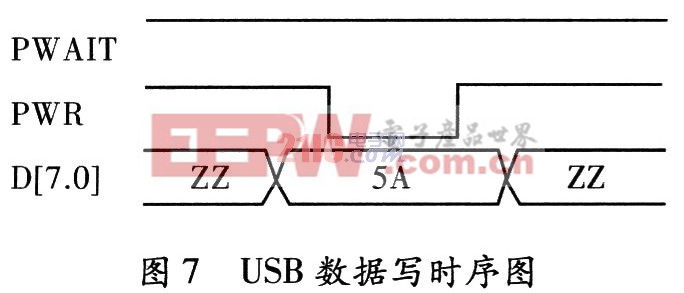

模塊1實現在地址IO模式下向寄存器寫數據。寫時序如圖7所示。可以根據地址線和PWR信號實現對某寄存器的寫控制。本文引用地址:http://www.104case.com/article/195456.htm

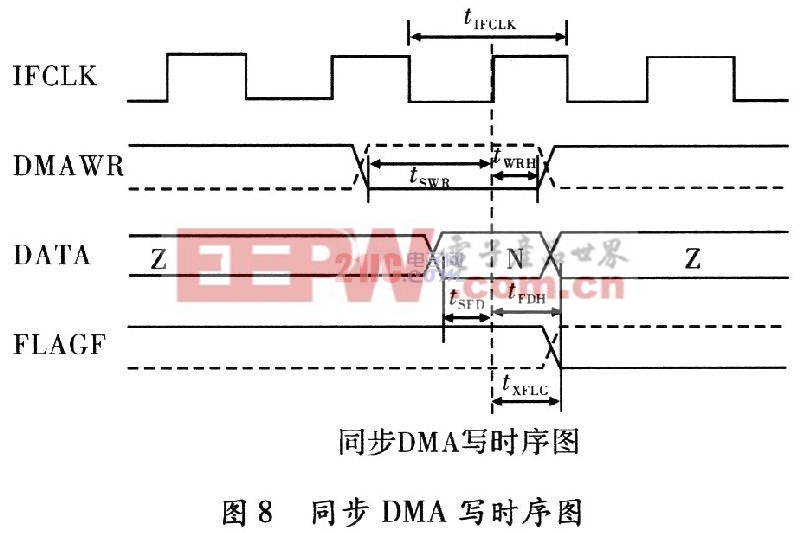

模塊2實現在DMA模式下FPGA向主機的批量數據傳輸。同步DMA的時序圖如圖8所示(時鐘由FPGA提供)。

本系統使用一個狀態機實現該功能,狀態機在“查找”和“傳輸”兩個狀態之間切換。系統啟動以后首先進入查詢FIFO的狀態,在查詢到FIFO中的數據量大于一個USB數據包(2 040 bit)時,狀態機進入到“傳輸”狀態。在“傳輸”狀態下,按照上述同步。DMA寫時序,首先傳輸6 bit包頭,然后傳輸2 040 bit數據,最后傳輸2 bit數據校驗。在數據傳輸的過程中,電路要一直查詢DMAING的狀態,檢測到:DMAING為低時要暫停數據傳輸。在傳輸完2 kB數據后,狀態機再轉入到“查詢”狀態,進行下一輪數據傳輸狀態。

系統當前的工作時鐘為20 MHz,在USB接口處可以達到的最大帶寬約為10 MB,系統分頻給A/D的時鐘為5 MHz,這樣可以保證A/D接口的最大帶寬達到3 MB。在Flash接口處的帶寬約為5 MB。將時鐘速度提升l倍,則USB口的傳輸能力可以達到約20 MB。

數據處理與儲存模塊主要是FPGA將高速A/D采集到的數據進行打包、暫存。本套電路中使用了一片由,TI公司生產的高速靜態RAM IS61-LV51216作為數據暫存器件;由FPGA對這片RAM存儲器進行監控。

4 結束語

采用USB協議的數據采集卡可以滿足對數據進行多通道的高精度采集、處理和傳輸,在數據有效采集的情況下,擺脫了對端口的依賴。

評論