基于USB的高精度多通道數(shù)據(jù)采集卡設(shè)計(jì)

由于USB通信是本系統(tǒng)設(shè)計(jì)主要的任務(wù)目標(biāo),所以在設(shè)計(jì)時(shí)也充分考慮到系統(tǒng)的可擴(kuò)展性,所有的信號(hào)引腳都有排線引出,方便了測試和擴(kuò)展。本文引用地址:http://www.104case.com/article/195456.htm

3 FPGA邏輯電路

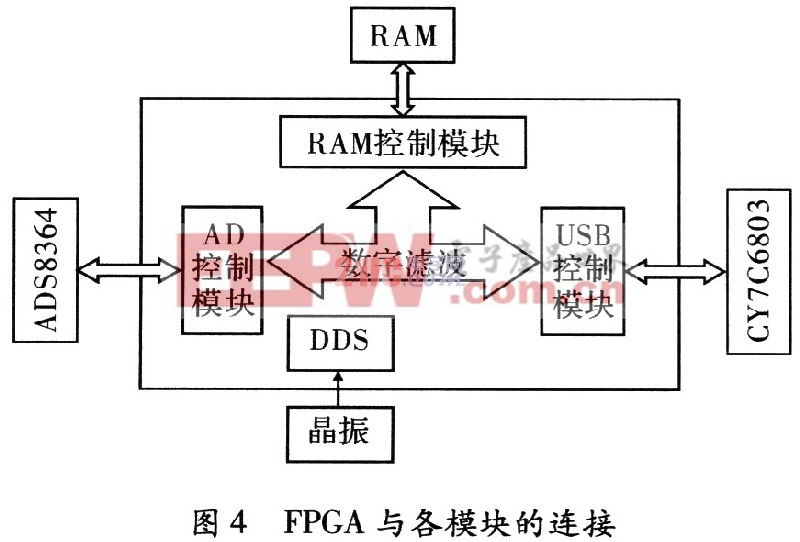

圖4為采集傳輸系統(tǒng)中FPGA與各模塊的連接。

整個(gè)電路選用Altera公司推出的新一代低成本的Cyclone系列FPGA器件EPlC6Q240作為控制和信號(hào)處理芯片。EPlC6Q240型FPGA芯片具有強(qiáng)大的硬件邏輯功能,總邏輯單元達(dá)5 980個(gè),有I/O引腳181個(gè),92 160位的內(nèi)部存儲(chǔ)單元,20個(gè)RAM單元,2個(gè)鎖相環(huán)。利用這些強(qiáng)大的功能,可以很容易進(jìn)行模塊控制和數(shù)據(jù)動(dòng)態(tài)濾波。如圖4所示,通過FPGA對(duì)A/D進(jìn)行采樣控制,將A/D采樣的數(shù)據(jù)進(jìn)行數(shù)字濾波后傳送到RAM中進(jìn)行,或是直接通過USB模塊將數(shù)據(jù)床送到電腦中進(jìn)行處理。

采用VerilogHDL硬件語言編程來對(duì)A/D采集,RAM傳輸,USB傳輸?shù)冗M(jìn)行控制信號(hào)輸出,并對(duì)采樣的數(shù)據(jù)進(jìn)行數(shù)字濾波。

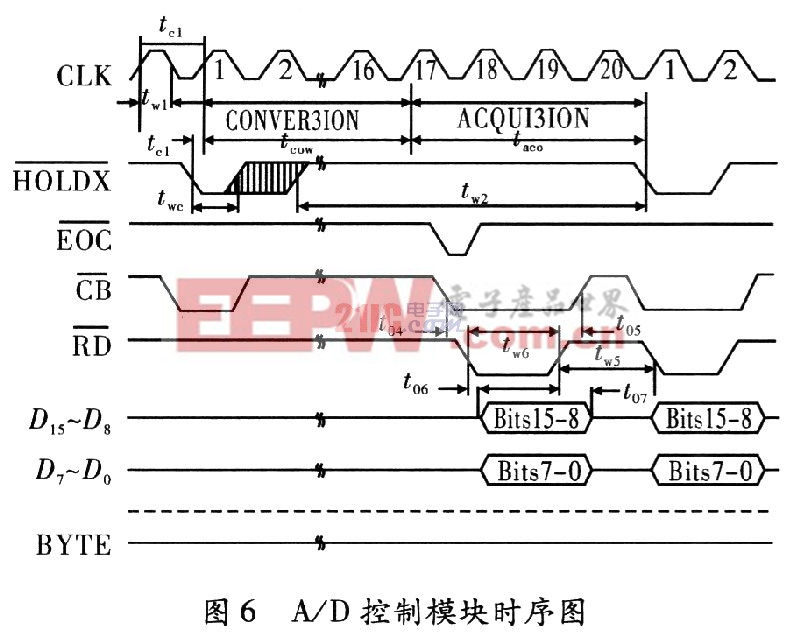

A/D數(shù)據(jù)接口模塊實(shí)現(xiàn)對(duì)ADS8364數(shù)據(jù)的采樣,采樣后的數(shù)據(jù)進(jìn)行濾波處理。本模塊對(duì)ADS8364的控制引腳有:

(1)模擬采樣通道控制信號(hào)為/HOLDA,/HOLDB,/HOLDC;

(2)數(shù)據(jù)輸出模式以及通道選擇信號(hào)為A0,A1和A2;

(3)讀控制信號(hào)為/RD。

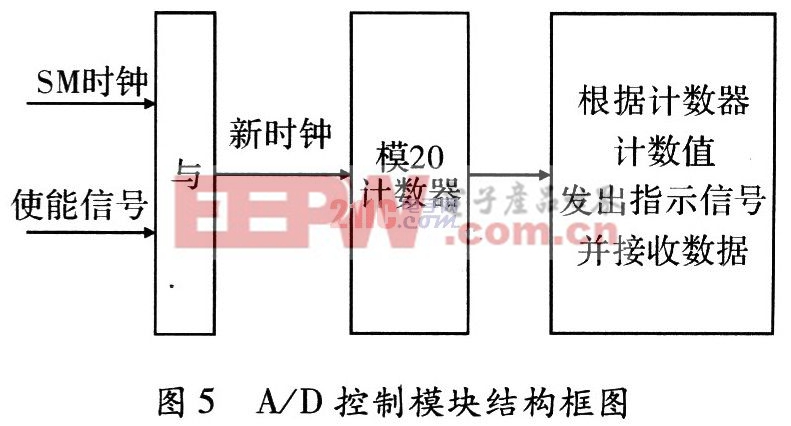

首先將5 MHz時(shí)鐘和使能信號(hào)相與產(chǎn)生新時(shí)鐘,使用該時(shí)鐘驅(qū)動(dòng)一個(gè)20個(gè)狀態(tài)的狀態(tài)機(jī)。在計(jì)數(shù)器值為15時(shí)將HOLDa,HOLDb,HOLDc置0,啟動(dòng)一次數(shù)據(jù)采樣。在計(jì)數(shù)值為2~3,4~5,6~7,8~9,10~ll,12~13且相應(yīng)的通道得到使能時(shí),分別發(fā)出通道l至通道6的通道地址。在計(jì)數(shù)值為3,5,7,9,ll,13時(shí)發(fā)出讀信號(hào)讀取相應(yīng)通道的數(shù)據(jù)。在計(jì)數(shù)值為15時(shí)發(fā)出采樣完畢信號(hào),指示6通道數(shù)據(jù)已經(jīng)采集完畢。

USB控制電路分兩個(gè)模塊完成。模塊1實(shí)現(xiàn)主機(jī)向FPGA寄存器單元的配置,模塊2實(shí)現(xiàn)FPGA向主機(jī)的數(shù)據(jù)包輸出。

評(píng)論