基于USB2_0和DDR2的數據采集系統設計與FPGA實現

摘要: 采用DDR2 SDRAM作為被采集數據的緩存技術, 給出了USB2.0與DDR2相結合的實時、高速數據采集系統的解決方案, 同時提出了對數據采集系統的改進思路以及在Xilinx的Virtex5 LX30 FPGA上的實現方法。

0 引言

隨著計算機、微電子和嵌入式系統技術的發展, 數據采集技術已經在生物醫學、圖像處理、雷達系統等眾多領域得到廣泛應用。本文設計的高速數據采集系統是應用于芯片現場測試的實時數據采集系統, 由于被測試芯片為250 MHz 8 bit的高速AD輸出, 因此, 該數據采集系統的數據采集率是2 Gbps。為了達到實時、高速、海量的數據采集, 該系統利用DDR2 SDRAM的高速數據傳輸能力和海量存儲能力做為采集數據的緩存,然后通過具有即插即用、易擴展、傳輸速率較高等特點的USB2.0接口來將DDR2 SDRAM中的數據傳輸到計算機中進行存儲和分析。

1 數據采集系統架構

該數據采集系統的總體架構由硬件部分、固件部分和計算機上的USB驅動及應用程序等幾大部分組成, 本文完成了硬件和固件部分的設計。

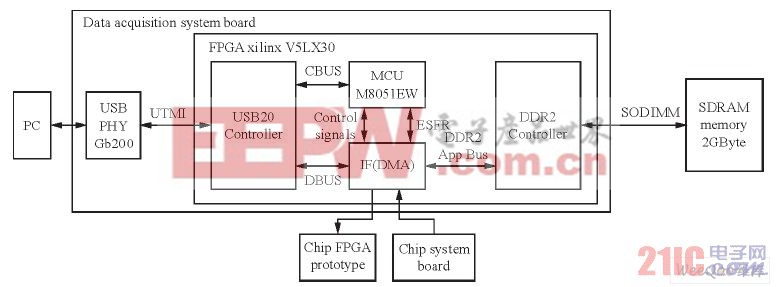

該系統的硬件部分主要由USB2.0、DDR2SDRAM、MCU以及IF等核心模塊組成, 圖1所示是其系統架構圖。

系統總體架構圖

圖1 系統總體架構圖

USB2.0由控制器和物理傳輸層組成, 其中控制器是在FPGA上實現的Faraday公司的IP核, 物理層可選用SMSC公司的GT3200芯片, 控制器與物理層芯片之間可通過標準的UTMI接口相連。

DDR2 SDRAM控制器是基于Xilinx公司提供的IP核, 工作頻率是125~266 MHz, 與SDRAM之間的接口是64 bit SODIMM筆記本內存條接口。作為數據存儲的SDRAM 是Samsung 公司的M470T5663QZ3-CE6 2GB 內存條。系統的控制核心MCU采用Mentor Graphics公司的增強型8051 IP核M8051EW, 該8051核采用兩個時鐘周期為一個機器周期的高性能架構, 同時支持MWAIT信號來控制程序總線, 從而能夠支持慢速的外部程序和數據存儲器。IF模塊是該系統設計的關鍵, 它相當于DMA的功能, 主要負責USB與DDR2、外部數據接口與DDR2之間的數據傳輸。

2 數據采集系統設計

本文中的數據采集系統采用USB2.0和DDR2SDRAM相結合的設計思路, 從而打破了傳統數據采集系統在實時數據采集中大容量和高速率不可兼得的瓶頸。在圖1所示的系統架構的四個部分中, 由于USB2.0和DDR2控制器都是IP核, 因此, 該系統設計的關鍵在于MCU和IF模塊。

2.1 MCU的設計

MCU是數據采集系統的控制核心, 主要用于對USB2.0控制器進行配置、查詢和處理USB事務, 以及解析USB設備請求, 同時, 還需配置IF模塊, 處理與IF模塊之間的控制信號等, 因此,MCU的設計包括數據接口及控制信號的設計以及固件設計兩個部分。

MCU數據總線接口包括與USB2.0控制器和與IF模塊的接口, 這里的USB2.0控制器和IF模塊相當于外部設備掛在MCU的外部存儲器總線和ESFR(外部特殊功能寄存器) 總線上。控制信號主要用于計算機上的控制臺控制IF模塊數據傳輸的開始與結束, 通常包含在USB的設備請求中。

整個固件的開發可在Keil C下完成, 并可通過JTAG進行調試。開發一般包括三部分: 一是協助USB控制器完成總線列舉過程, 讓計算機識別USB設備; 二是通過解析自定義USB設備請求,來對采集模式、深度等進行配置, 從而控制采集的開始與結束; 三是查詢和處理IN、OUT事務中斷, 并控制USB數據傳輸。

評論