基于FPGA的數據采集系統的設計與實現

2 數據采集系統軟件設計方案

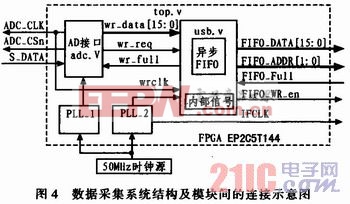

FPGA軟件設計方案中采用了自頂向下的設計方法,運用Verilog HDL語言來設計數字系統,分別完成數字系統內部各個子模塊的設計。數據采集系統結構及模塊間的連接示意圖如圖4所示。

由圖4可見,系統主要由3個模塊組成。它們分別是A/D接口adc.v模塊、USB接口usb.v模塊以及頂層top.v模塊,其中在頂層top.v模塊中,完成了對其他兩個模塊的調用,使它們拼接成為一個完整的系統。其中鎖相環PLL_1和PLL_2分別給ade.v模塊和usb.v模塊提供時鐘源。

2.1 FPGA控制A/D芯片接口的軟件設計

在adc.v模塊中,需要完成FPGA對TLV1572的接口邏輯代碼的設計,其實質就是在TLV1572的時序分析的基礎上來設計邏輯代碼,使得FPGA能夠按照其時序要求完成對A/D芯片的各種控制,包括提供給TLV1572的串行時鐘信號信號ADC_CLK、CS片選信號ADC_CSn以及從TLV1572中讀取出轉換完成的串行數據S_DATA。

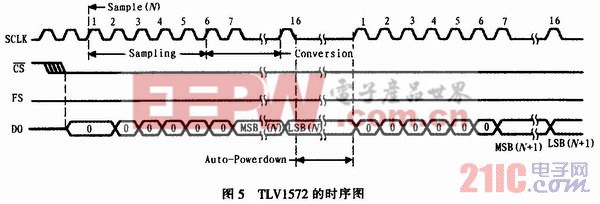

TLV1572的時序圖如圖5所示。

從時序圖可見,A/D芯片的轉化過程是在當CS為低電平后,由SCLK的上升沿發起的,輸出的頭六位二進制數字均為“0”,此時A/D芯片正處于采樣階段,數字無效,這六位無效的二進制數之后,A/D轉換完成后的二進制數據在SCLK的上升沿被送到總線上,這時,作為系統主控制芯片的FPGA應當去采樣總線上的數據,得到轉換后的結果。

2.2 FPGA控制USB2.0芯片的軟件設計

在usb.v模塊中,需要完成FPGA對CY7C68013A的接口邏輯代碼的設計和異步FIFO模塊的設計。其中,對CY7C68013A的接口邏輯代碼主要是完成對CY7C68013A芯片的端點FIFO的各種控制,包括16位的數據信號FIFO_DATA[15:0]、2位端點FIFO選擇信號FIFO_ADDR[1:0]、端點FI-FO滿標志位信號FIFO_Full、端點FIFO寫使能信號FIFO_WR_en。因為adc.v模塊和芯片外部的CY7C68013A工作在不同的時鐘域內,故異步FIFO模塊設計部分設計的目的除了是要完成從ade.v模塊讀取過來數據的緩沖,另外就是需要解決異步時鐘域數據傳輸可能出現的亞穩態問題。

具體來說,FPGA在工作時需要不斷向CY7C68013A的端點FIFO寫入數據,而FPGA與CY7C68013A之間的工作模式屬于同步方式,兩者都由PLL _2模塊提供40 MHz的時鐘信號進行工作,那么它們之間的關系就是同步Slave FIFO的寫操作,由FPGA向CYTC68013A中寫入數據。

在Verilog HDL程序設計中,需要設計一個狀態機來完成同步Slave FIFO寫的時序,寫時序如下;1)IDLE:當寫事件發生時,進狀態1;2)狀態1:使FIFOADR[1:0]指向IN FIFO,進狀態2;3)狀態2:如果端點FIFO滿,在當前狀態等待,否則進狀態3;4)狀態3:驅動數據到數據線上,使SLWR有效,持續一個IFCLK周期,進狀態4;5)狀態4:如需傳輸更多的數,進狀態2,否則進入IDLE狀態。

該狀態轉換的狀態圖如圖6所示。

評論