基于PCI ExPress總線傳輸的視頻采集系統方案

3.2 FPGA

3.2.1 FPGA器件選型

FPGA型號的選擇主要基于以下方面考慮:具有PCIExpress總線;通道不低于x8;具有嵌入式微處理器;合適的I/O管腳數和資源,支持所需的電平標準;具有較低的功耗;合適的性價比。

因此,選擇Xilinx公司的Virtex-5系列的XC5VFX3-0T,封裝為FF665 PCI Express總線;具有PowerPC440嵌入微處理器。配置芯片選用容量為1 GB的CF卡。

3.2.2 FPGA的性能和資源

1)時鐘資源32條全局時鐘總線,對整個器件上的所有資源進行時鐘控制,且可以驅動邏輯信號;

2)時鐘管理技術 時鐘去歪斜、頻率合成、相移和動態重配置等功能;

3)鎖相環作為廣譜頻率的頻率合成器,并且與CMT的DCM配合作為外部或內部時鐘的抖動濾波器;

4)BLOCK RAM 2 448 Kb,可配置為RAM、雙口RAM和FIFO等,且其內容能夠初始化;

5)可配置邏輯塊 實現組合邏輯和時序邏輯的主要資源;

6)SelectIO資源 可支持種類繁多的標準接口。包括輸出強度和斜率的可編程控制以及實現數控阻抗的片上終端;

7)SelectIO邏輯資源 包括組合輸入/輸出、三態輸出控制、寄存輸入/輸出、寄存三態輸出控制、DDR輸入/輸出和DDR輸出三態控制;

8)高級SelectIO邏輯資源 輸入串并轉換和輸出并串轉換;

9)DSP邏輯片 64個550 MHz DSP48E slice,每個DP48E包括1個28x18的乘法器、1個加法器和1個累加器。利用XILINX ISE的FPGA Edit也可觀察FPGA的內部結構。

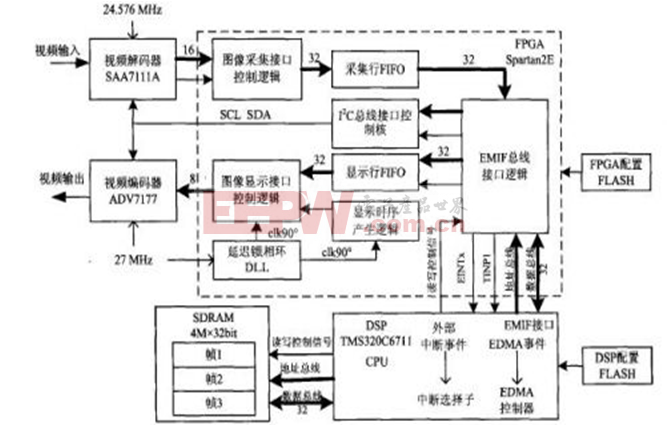

3.3 數據緩存

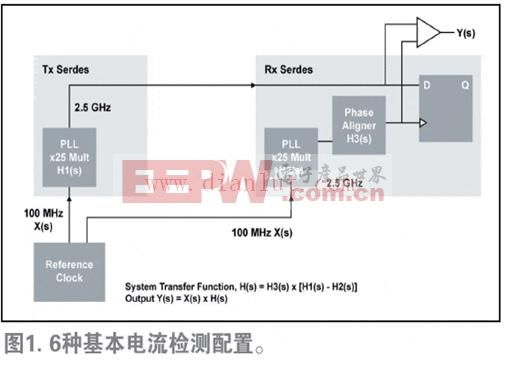

由于PCI Express的總線波特率為2.5 Gbps,遠大于1路采集后的數字視頻信號。當視頻數據經并行總線傳入FPGA內,通過配置為異步輸入輸出的FIFO進行數據緩存,提高總線使用效率。如果PCI Express總線為×1通道,PAL制式視頻轉換為常用的8位4:2:0的YUV格式數字視頻,按照PCIExpress總線傳輸有效數據1.62 Gb/s計算,理論上可以傳輸36路。

3.4 FCI Express接口實現

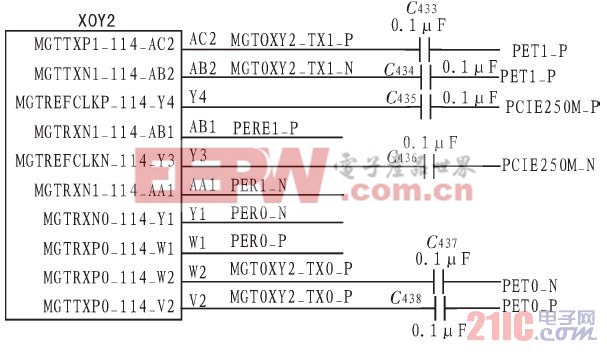

利用具有PCI Express的FPGA來設計,選用Xilinx公司的Virtex-5 LXT系列的FPGA,利用其內的PCI Express IP核進行設計,完成功能如下:用戶接口的本地鏈路成幀接口;64位數據總線寬度與3位提醒總線;包化接口,帶用于標記包的幀起始(SOF)和幀結束(EOF);傳輸和接收方向用戶接口的包中斷特性;幀錯誤檢測支持;多通道配置支持:×1、×2、×4和×8;這里通道配置為×1;每通道1.62 Gb/s或更高的吞吐量;利用集成端點模塊中的自動協商功能,可以在某些通道不能工作時使設計使用較低的帶寬;物理層中使用的8B/10B解碼和解碼。此方案雖開發難度大、周期長,但具有外電路圍簡單,硬件成本低,設計靈活、集成度高且易升級等特點。其接口電路如圖3所示。

圖3 PCI Express接口電路

3.5 時鐘

本設計需要4個時鐘信號,其中視頻解碼信號的時鐘要求最高,時鐘精度必須在±50 ppm以內,其次為PCI Express總線工作的時鐘頻率。在FPGA內對時鐘信號進行了DCM和PLL處理,完成了對時鐘信號的去歪斜、相移和頻率合成等功能。

3.6 Flash和DDRSDRAM

為使設計具有靈活性、擴展性和升級性,預留了Flash和SDRAM來存儲程序和運行程序,滿足智能性和易于以太網遠程控制等要求。

3.7 以太網接口電路

通過FPGA+PHY+變壓器組成以太網接口電路,可以用此接口加載程序,也可用此接口和互聯網連接。利用XILINX公司的FPGA開發軟件ISE,通過FPGA內IP核按照TriMode Ethemet MAC進行。

3.8 DMA傳輸

本設計采用DMA方式進行數據內部傳輸。數字視頻信號經并行總線傳入FPGA內,通過FIFO進行數據緩存,經DMA方式,通過PCI Express傳給計算機。

評論