基于DSP的抖動測量的方案

引言

本文引用地址:http://www.104case.com/article/194930.htm抖動(jitter)會使數字電路的傳輸性能惡化,由于信號上升沿或是下降沿在時間軸上的正確位置被取代,在數據再生的時候,數據比特流中就會引入錯誤。在合并了緩沖存儲器和相位比較器的數字儀表中,由于數據溢出或是損耗,錯誤就會引入到數字信號中。此外,在數模變換電路中,時鐘信號的相位調制會使恢復出的采樣信號惡化,這在傳輸編碼的寬帶信號時會造成問題。

1 抖動的分類

抖動分為系統抖動和隨機抖動。

(1)系統抖動是在信號再生電路時間上不準,或是碼是串擾,或是在幅頻轉換中的不準確的電纜均衡造成的。系統抖動取決于系統的性能。

(2)隨機抖動來源于內部或是外部的干擾信號,如噪聲、串擾、反射等。隨機抖動與傳輸信號的系統無關。

系統抖動與不同的脈沖再生電路的脈沖的模式有關,會連續地積累。隨機抖動則與脈沖再生電路的脈沖模式無關,而且也不會連續地積累;在大多數低速率的數字系統中,系統抖動占主導地位;而在高速系統中,隨機抖動變得越來越重要,甚至會占據主導地位。

干擾性的抖動可以利用信號再生電路劃中利用“去抖動”電路來減弱其影響。這種“去抖動”電路來減弱其影響。這種“去抖動”電路包括了一個帶有窄帶相位平滑電路的信號緩沖器。信號再生電路只能將抖動頻率高于時鐘再生電路的截止頻率的抖動成分減小,而低頻的抖動成分則仍然會出現在輸出信號或是信號再生電路中。在這種情況下,抖動被傳輸到輸出信號中,信號再生電路此時就象是一個低通濾波器。

2 抖動測量方法

傳統的抖動測量采用模擬測試的方法。圖1給出了傳統模擬測量方法的原理框圖,它是將數據信號與基準時鐘信號相比較,使用相位探測器的平均輸出。模擬測量方法帶來了很多問題,這都是因為相位探測器將相位表達成一個模擬電壓引起的。

2.1 用模擬方法測試抖動的缺點

a 時鐘恢復限制了抖動測量的帶寬;

b 時間恢復由于自由運行頻率的偏移引入了抖動噪聲;

c 大動態范圍要求大頻率分割,導致產生了起出相位探測器范圍的低頻脈沖,進一步限制了測量的帶寬;

d 模擬電壓受制于由噪聲和寄生電容產生的負面影響;

e 模擬電壓的范圍受制于電源電壓的范圍;

f 基準恢復由于其帶寬小獲得鎖相很慢。

隨著DSP技術、ADC應用技術和ASIC技術的發展,抖動分析跟隨著科技從模擬到數字的轉變進程,發展了基于數字分析的抖動測量方法。基于數字的抖動分析方法有先進得多的特性,能使工程師們為下一代設計的測試和分析作更充分的準備。

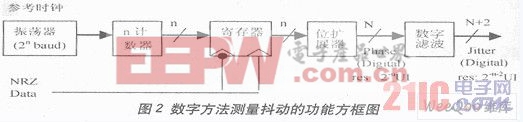

下面圖2給出了基于數字分析的抖動測量方法的原理框圖。這里的目標是將每個NRZ沿用二進制數作時間標記,其中計數器最低位(LSB)權值就是時間間隔分辨率。時間間隔計數器完成時間標記功能,通過數字處理標記出抖動大小,再經過數字濾波器提供抖動測量所需的高通和低通濾波。在濾波過程中,可實現分辨率中兩個最佳位。抖動得到進一步的處理以檢測峰峰值、真有效值或其它參數,比如頻譜容量。

評論