基于FPGA的智能變送器的設計與實現

3 系統軟件設計與仿真

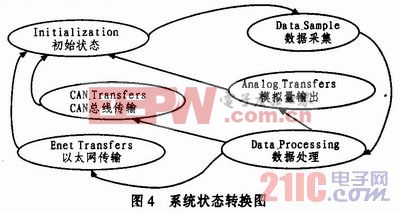

該系統以XILINX公司的XC3S4005PQ208C作為中央處理器,整個系統主要包括初始狀態(Initialization)、數據采集狀態(Data_Sample)、數據處理狀態(Data_Processing)、以太網傳輸狀態(Enet_Transfers)、CAN總線傳輸狀態(CAN_Transfers)、和模擬輸出狀態(Analog_ Transfers)等6種狀態,因此,可以利用有限狀態機的設計方案來實現。其狀態轉換圖如圖4所示,通過開發工具ISE10.1對各個模塊的VHDL源程序及頂層電路進行編譯、邏輯綜合,電路的糾錯、驗證、自動布局布線及仿真等各種測試,最終將設計編譯的數據下載到芯片中即可。

初始狀態:實現系統初始化;數據采集狀態:完成數據采集過程;數據處理狀態:對采集的信號進行一系列的濾波處理,非線性校正等;以太網傳輸狀態,CAN總線傳輸狀態:根據實際需要將信號數字輸出;模擬輸出狀態:進行數模轉換,輸出標準的電壓電流信號。

3.1 數據采集的FPGA設計

數據采集是工業測量和控制系統中的重要部分,它是測控現場的模擬信號源與上位機之間的接口,其任務是采集現場連續變化的被測信號。對數字系統來說,數據采集主要由傳感器放大電路和A/D轉換電路構成,由硬件電路可見,系統通過AD7264模/數轉換器來實現模/數轉換。AD7264內含6個寄存器,分別是A/D轉換器的結果寄存器、控制寄存器、A/D轉換器A和B的內部失調寄存器、A/D轉換器A和B通道的外部增益寄存器。由于XC3S4005PQ208C和AD7264都兼容SPI接口,兩者的編程只需按照時序圖進行即可。AD7264與FPGA的接口主要包括PD0數據輸入選擇端:DoutA(DoutB)兩路數據輸出端;OUTa(OUTb)兩路數據輸入端;CoutA(CoutB、CoutC、CoutD)比較器輸出;G3(G2、G1、G0)四路增益控制輸入信號。增益由控制寄存器的低四位控制;ADSCLK時鐘信號;ADCS片選信號,低電平有效。AD7264工作頻率為20 MHz,在CS下降沿,跟蹤保持器處于保持模式。此時,采樣、轉換同時被初始化模擬輸入。這需要至少19個SCLK周期。第19個SCLK的下降沿到來時。AD7262恢復至跟蹤模式,并設置DOUTA、DOUTB為使能。數據流由14位組成,MSB在前。圖5為AD7264讀寄存器時序仿真圖。

評論