鎖相時鐘可抑制串模干擾

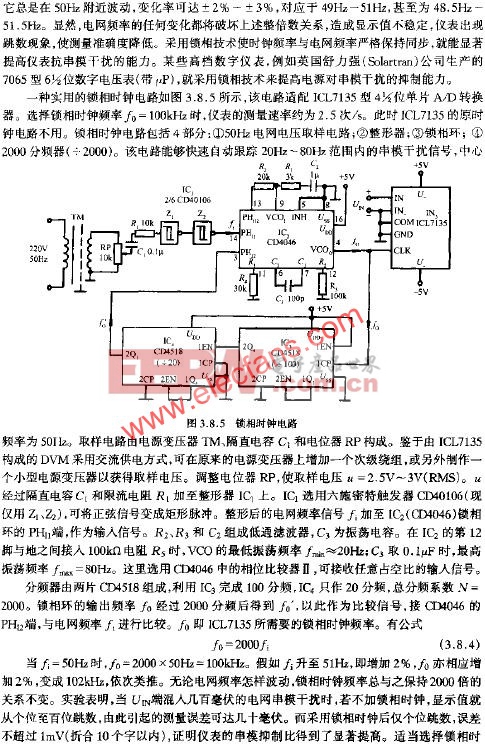

目前廣泛使用的3 1/2~5 1/2位數字電壓表(DVM),大多選用雙積分式或多重積分式單片A/D轉換器。其優點是電路簡單,抗串模干擾能力強,成本較低。只要設計的時鐘頻率F0恰好等于50HZ的整倍數,電網串模干擾就被完全抑制掉了。然而電網頻率實際上并不穩定,

本文引用地址:http://www.104case.com/article/194382.htm

鐘頻率,還可配MAX133/MAX134、HI7159型4 3/4~5 1/2位單片A/D轉換器使智能數字電壓表的電磁兼容性得到改善。

評論