基于A/D和DSP的高速數據采集系統方案介紹

采樣時,通過程序使DX和FSX輸出為1。此時采樣脈沖與DX、FSX相“與”后被分別送人AD6644的時鐘輸入ENCODE和IDT72V253的寫時鐘輸入WCLK,A/D轉換器開始工作,且不斷將轉換數據送至自己的輸出口D0~D7。當寫使能WEN為低時,A/D轉換器輸出口上的數據在WCLK的上升沿被依次寫入FIFO。A/D轉換器和FIFO每來一次脈沖,便完成一次模數轉換并把數據順序存人FIF。使IDT72V253的LD為低、FSELO為高、FSEL1為高時,IDT72V253經過主復位后,偏移值n、m為默認值63,每個雷達回波脈沖采樣63個點后,存儲器幾乎滿標志PAF輸出低電平(在未到63時輸出高電平)。把此標示接到TMS320C6713的外部中斷INT0上,利用它由高到低的變化產生中斷,以表明一組數據采集完成。本文引用地址:http://www.104case.com/article/194344.htm

在中斷中,DSP首先迅速關閉采樣脈沖信號(使DX和FSX的輸出為0),停止A/D轉換器和F1FO的工作。TMS320C6713的CE0和ARE相“與”后與FIFO的讀輸入RCLK接在一起,DSP每執行一次I/O讀操作,R=CE0十ARE便向RCLK發出一脈沖,把FIFO讀使能PEN置為低,同時連續執行63次I/O讀操作,數據便依次從IDT72V253送入TMS320C6713,整個數據采集工作就此完成。在進行第二次數據的采集前,最好將IDT72V253先復位,把TMS320C6713通用緩沖串口的CLKX配置為通用輸出口,給IDT72V253的PRS引腳輸入一個不小于10 ns的低脈沖,即在DSP的CLKX引腳輸出一個低脈沖。這樣可以更充分地保證FIFO的讀、寫指針的穩定。

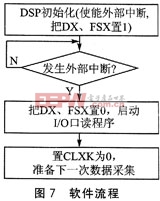

3.3 軟件設計

軟件設計包括CPLD和DSP兩個部分。CPLD程序用VHDL語言編寫,實現簡單的邏輯轉換功能,程序設計比較簡單。DSP編程中有幾個關鍵步驟:外部中斷使能、時鐘送入A/D轉換器和FIFO、等待中斷、停止A/D轉換器和FIFO、采集數據、復位FIFO。整個軟件流程如圖7所示。

4 結 論

通過實際設計表明,在DSP高速數據采集系統中,采用FIFO器件作為A/D轉換器與DSP之間的橋梁,可以根據具體需要靈活設置FIFO的各個標志,使其具有很強的外部接口能力;并且通過軟件很容易調整A/D轉換器、FIFO和DSP的操作時序,增強了操作的靈活性,起到了很好的數據緩沖作用,保證了數據采集的安全可靠。系統硬件具有結構簡單、性能可靠的特點;軟件具有控制靈活、程序調試方便等優點。

評論