可降低下一代IC測試成本的確定性邏輯內置自測技術

20世紀70年代隨著微處理器的出現,計算機和半導體供應商逐漸認識到,集成電路需要在整個制造過程中盡可能早地進行測試,因為芯片制造缺陷率太高,不能等到系統裝配好后再測試其功能是否正確,所以在IC做好之后就應對它進行測試,一般在自動測試設備上采用仿真完整系統激勵和響應的功能測試方案進行。

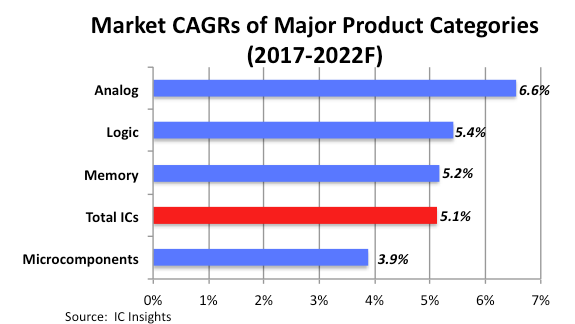

本文引用地址:http://www.104case.com/article/193853.htm功能測試使制造過程更加經濟高效,因為可以保證裝配好的電路板和系統都是由已知完好的部件構成,所以成品工作正常的可能性更高。功能測試代表了第一代IC測試,廣泛應用了近二十年。隨著電子產品越來越復雜專業,專用集成電路(ASIC)成為數字測試的重點,這種電路的開發周期更短,需要新的測試方法。

20世紀90年代初期,創建一套能滿足缺陷覆蓋率水平的功能測試方案成本非常高昂,而且開發工作單調乏味,此時掃描測試顯示出明顯的優勢,它具有可預測覆蓋范圍自動測試方案生成(ATPG)功能。與集成可測性設計(DFT)合在一起,設計人員能于設計早期保證其設計是高度可測的,且滿足嚴格的質量要求,沒有過多技術性工作,也不會造成計劃延遲。在過去十年,這種從功能測試到掃描測試的轉變代表IC測試走向了第二代。

新型系統級芯片測試方法

如今整個系統都能放在一個芯片上,百萬門SoC產生的新挑戰帶來了對第三代數字測試的需求。最根本的問題與經濟效益有關,即設計人員和測試工程師應如何應用掃描測試,既達到可預測高覆蓋率,同時制造成本低且對設計影響最小?之所以有這種要求的原因之一是如果要實現高覆蓋率測試,掃描測試的數據量將急劇增長。決定掃描測試數據的因素包括:

·掃描狀態元件總數

·目標故障位置總數

·被測故障模式的數量和復雜度

上述每個因素都會隨新一代硅片工藝技術進步而使最后的數據量大幅增加。把這些因素與芯片I/O的數量限制和速度增長,以及ATE通道的物理約束結合起來考慮時,會發現掃描測試時間和成本都將呈指數增長。

Synopsys確定性邏輯內置自測(DBIST)是高級系統級芯片測試DFT Compiler SoCBIST的一個很重要的功能,是一種有效數字邏輯測試方法,能提高測試質量,減少測試對設計人員的影響。它可以降低下一代集成電路測試成本,提高未來更大更復雜SoC設計的總體質量。

SoCBIST對一次通過測試綜合方案DFT Compiler進行了擴展,使設計人員在其設計中可直接實施可預測邏輯內置自測(BIST),而不會影響設計的功能、時序或電源要求。DBIST提供了一整套功能強大的BIST設計規則檢測(DRC)、綜合、集成、方案生成、驗證及診斷能力。

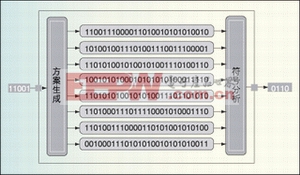

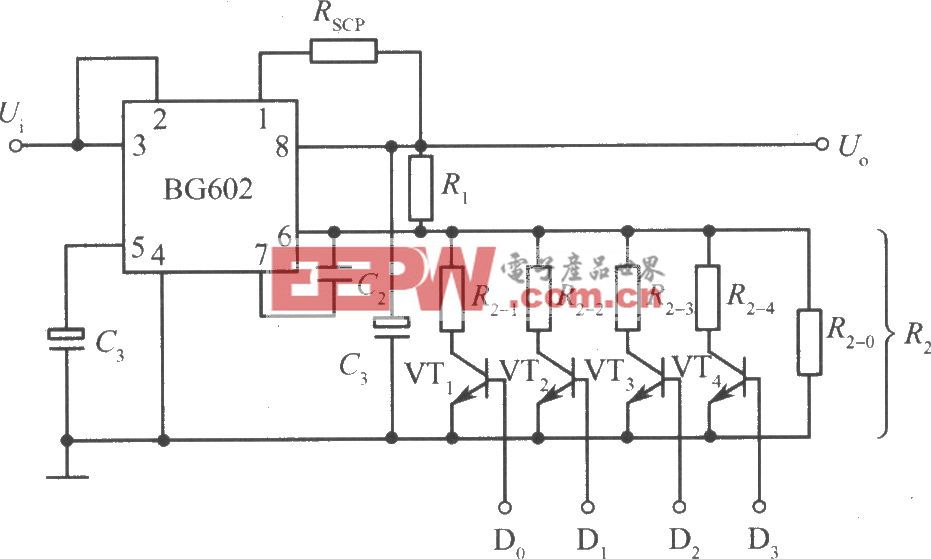

圖1是Synopsys確定性邏輯BIST的基本結構,它利用已有的邏輯BIST概念和技術實現下面幾個基本目標:

·支持大量并行內部掃描鏈路,從而將測試時間縮短至少一個數量級;

·把掃描測試數據編碼成BIST晶種(seed)與符號,使測試數據量減少幾個數量級;

·大幅減少所需測試引腳數。

盡管可以考慮其它更簡單的掃描壓縮技術,但都不能像邏輯BIST那樣降低整個測試成本。此外,邏輯BIST是未來測試復用和移植的理想環境,它可使為某一內核/模塊開發的測試也能應用于SoC/芯片級、板級和系統級測試當中。

傳統邏輯BIST解決方案已出現多年,但仍因為若干根本問題沒有得到廣泛的應用,包括:

·工具仍限定在設計流程,而不是一個綜合解決方案;

·覆蓋率取決于隨機邏輯BIST,這導致不可預測的設計影響和更低的測試質量;

·測試依賴于長時間自測,相對于在昂貴的ATE上的制造測試效率很低,只能預計故障檢測率;

·診斷成為事后諸葛亮,需要專用ATE接口,不能提供完整的信息確定缺陷的位置。

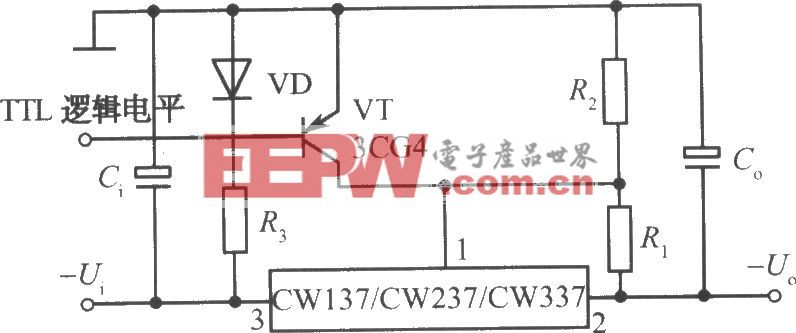

集成確定性邏輯BIST流程

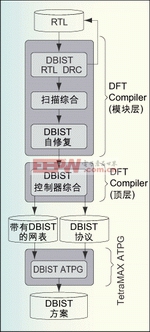

圖2是DBIST流程的主要步驟,和掃描DFT相比只額外多了幾步,設計或測試開發工藝中沒有引入新的迭代過程。該流程的關鍵是一組定義明確的邏輯BIST規則,作為寄存器轉移級(RTL)規則檢查基礎和與RTL綜合集成在一起的自動化規則沖突解決機制,DFT Compiler為掃描特性提供大量支持,所以DBIST方法對于現有大多數掃描流程只需要有一些簡單的增強即可。在綜合模塊水平上,增加的邏輯BIST規則只用于能傳播X值到符號分析儀的未控制節點,在其它掃描單元完成綜合后,對沖突節點提供全面的測試節點可控性;在頂層上,未連接到ATE進行DBIST測試的芯片引腳通過附加封包掃描單元對觀察進行控制。與傳統邏輯BIST不同的是,無需增加測試點就可提高隨機方案抵抗邏輯的可控性和可觀察性。

在設計頂層,DBIST控制器自動由DFT COMPILER合成、插入并連接到帶DBIST的模塊測試引腳上。為支持更大型設計,DFT Compiler可以使用掃描插入和帶DBIST模塊的“只測”模型,這些只測模型提供的容量幾乎無限,大大縮短了頂級DBIST綜合的運行時間。DBIST控制器幾乎不需要用戶輸入,可自動配置用于最后內部掃描鏈路結構,其流程是透明的,它處于DBIST解決方案的中心并幫助得到最后的結果。

DBIST控制器利用若干標準邏輯BIST元件實現高度優化測試系統,這些單元包括:

·一個或以上偽隨機方案發生器(PRPG),每個都由一個很寬的線性反饋位移寄存器(LFSR)和并行影子寄存器組成,以使晶種再植最優;

·一個或以上移相器,為內部掃描鏈路輸入提供統計獨立的PRPG值;

·一個或以上壓縮器,把內部掃描鏈路輸出數減少到1/4;

·一個或以上多輸入記號寄存器(MISR)以收集測試響應;

·一個DBIST狀態機和相關計數器。

除了所需邏輯BIST功能外,DBIST還支持4個單獨測試模式用于完整的制造測試程序:

評論